# **Signetics**

### **Linear Products**

### DESCRIPTION

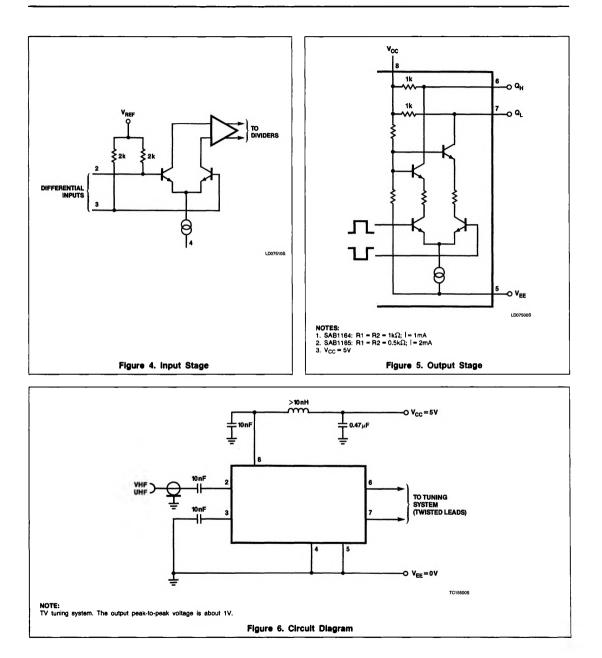

This silicon monolithic integrated circuit is a prescaler in current-mode logic. It contains an amplifier, a divide-by-64 scaler and an output stage. It has been designed to be driven by a sinusoidal signal from the local oscillator of a television tuner, with frequencies from 70MHz up to 1GHz, for a supply voltage of 5V  $\pm$  10% and an ambient temperature of 0 to 70°C. It features a high sensitivity and low harmonic contents of the output signal.

# SAB1164/65 1GHz Divide-by-64 Prescaler

PIN CONFIGURATION

8 V<sub>cc</sub>

7 0

6 QH

5 VEE

CD118805

IC IT

CI 2

C2 3

VEE 4

TOP VIEW

**Product Specification**

### FEATURES

- 3mV (typ) sensitivity

- Differential inputs

- AC input coupling; internally based

- Outputs edge-controlled for low RFI

- Power consumption: 210mW (typ)

- Mini-DIP package

- Low output impedance (SAB1165)

### APPLICATIONS

- PLL or FLL tuning systems, FM/ communications/TV

- Frequency counters

### **ORDERING INFORMATION**

| DESCRIPTION                 | TEMPERATURE RANGE | ORDER CODE |

|-----------------------------|-------------------|------------|

| 8-Pin Plastic DIP (SOT-97A) | 0 to +70°C        | SAB1164N   |

| 8-Pin Plastic DIP (SOT-97A) | 0 to +70°C        | SAB1165N   |

### **BLOCK DIAGRAM**

## 1GHz Divide-by-64 Prescaler

SAB1164/65

#### ABSOLUTE MAXIMUM RATINGS

| SYMBOL          | PARAMETER                                     | RATING               | UNIT |

|-----------------|-----------------------------------------------|----------------------|------|

| V <sub>CC</sub> | Supply voltage (DC)                           | 7                    | v    |

| VI              | Input voltage                                 | 0 to V <sub>CC</sub> | v    |

| TSTG            | Storage temperature range                     | -65 to +125          | °C   |

| TJ              | Junction temperature                          | 125                  | °C   |

| θ <sub>CA</sub> | Thermal resistance from crystal to<br>ambient | 120                  | °C/W |

### DC ELECTRICAL CHARACTERISTICS $V_{EE} = 0V$ (ground); $V_{CC} = 5V$ ; $T_A = 25^{\circ}C$ , unless otherwise specified.

The circuit has been designed to meet the DC specifications as shown below, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed-circuit board.

| CYMDOL                             |                                           |     | LIMITS |                                          | UNIT   |

|------------------------------------|-------------------------------------------|-----|--------|------------------------------------------|--------|

| SYMBOL                             | PARAMETER                                 | Min | Тур    | Max                                      | UNIT   |

| V <sub>OH</sub><br>V <sub>OL</sub> | Output voltage<br>HIGH level<br>LOW level |     |        | V <sub>CC</sub><br>V <sub>CC</sub> - 0.8 | v<br>v |

| Icc                                | Supply current                            |     | 42     | 50                                       | mA     |

#### AC ELECTRICAL CHARACTERISTICS $V_{EE} = 0V$ (ground); $V_{CC} = 5V \pm 10\%$ ; $T_A = 0$ to $+70^{\circ}C$

| SYMBOL              | PARAMETER                              | LIMITS |     |      |      |

|---------------------|----------------------------------------|--------|-----|------|------|

|                     |                                        | Min    | Тур | Max  | UNIT |

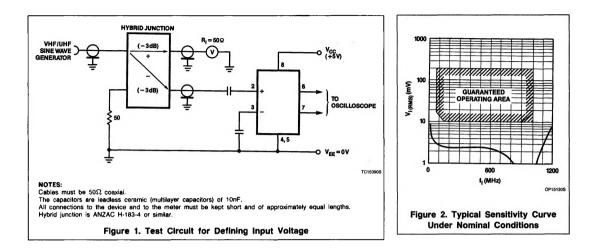

| VI(RMS)             | Input voltage RMS value (see Figure 2) |        |     |      |      |

|                     | input frequency 70MHz                  |        | 9   | 17.5 | m۷   |

|                     | 150MHz                                 |        | 4   | 10   | mV   |

|                     | 300MHz                                 |        | 3   | 10   | m۷   |

|                     | 500MHz                                 |        | 3   | 10   | m۷   |

|                     | 900MHz                                 |        | 2   | 10   | m۷   |

|                     | 1GHz                                   |        | 3   | 17.5 | m۷   |

| VI(RMS)             | Input overload voltage RMS value       |        |     |      |      |

|                     | input frequency range 70MHz up to 1GHz |        |     | 200  | mV   |

| V <sub>O(P-P)</sub> | Output voltage swing                   | 0.8    | 1   |      | v    |

|                     | Output resistance                      |        |     |      | 1.1  |

| Ro                  | SAB1164                                |        | 1   |      | kΩ   |

| Ro                  | SAB1165                                |        | 0.5 |      | kΩ   |

| ΔVo                 | Output unbalance                       |        |     | 0.1  | v    |

|                     | Output rise time <sup>1</sup>          |        |     |      |      |

| t <sub>TLH</sub>    | f <sub>l</sub> = 1GHz                  |        | 25  |      | ns   |

|                     | Output fall time <sup>1</sup>          |        |     |      |      |

| t <sub>THL</sub>    | $f_{I} = 1 GHz$                        |        | 25  | 1    | ns   |

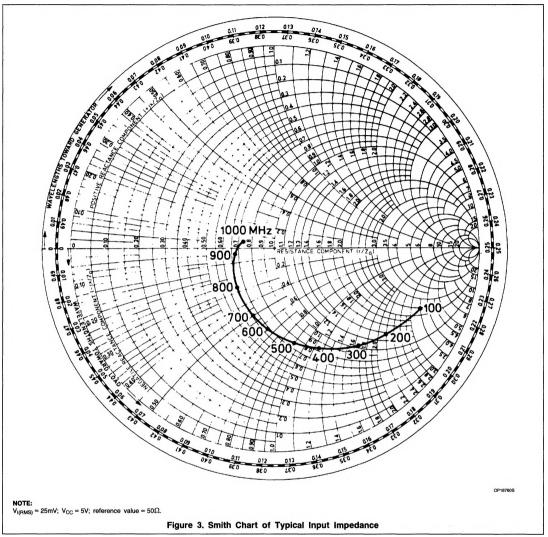

NOTE:

1. Between 10% and 90% of observed waveform.

#### FUNCTIONAL DESCRIPTION

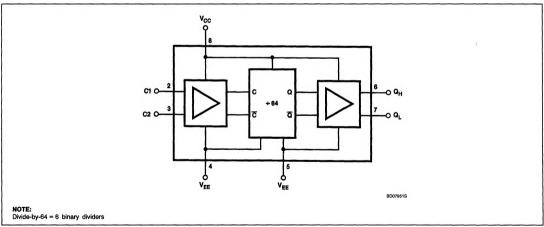

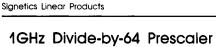

The circuit contains an amplifier, a divide-by-64 scaler and an output stage. It has been designed to be driven by a sinusoidal signal from the local oscillator of a TV tuner, with frequencies from 70MHz up to 1GHz, for a supply voltage of 5V  $\pm$  10% and an ambient temperature of 0 to  $\pm$  70°C. The inputs are differential and are internally biased to permit capacitive coupling. For asymmetrical drive the unused input should be connected to ground via a capacitor.

The first divider stage will oscillate in the absence of an input signal; an input signal within the specified range will suppress this oscillation. The output differential stage has two complementary outputs. The output voltage edges are slowed down internally to reduce the harmonic contents of the signal.

Wide, low-impedance ground connections and a short capacitive bypass from the  $V_{CC}$  pin to ground are recommended.

## 1GHz Divide-by-64 Prescaler

SAB1164/65

# SAB1164/65

**Product Specification**

## 1GHz Divide-by-64 Prescaler

SAB1164/65