# Step-Down Switching Regulator with Current-Mode Control

# **Features and Benefits**

- Current-mode control system employed

- Excellent line regulation (60 mV maximum)

- 165 mΩ maximum on-resistance of built-in MOSFET

- Output current 3.5 A

- Wide range of input voltages (4.75 to 28 V), supports 24 V direct drive

- Output voltage 0.5 to 24 V, compatible with various IC power supply voltages, through low V<sub>REF</sub> of 0.5 V.

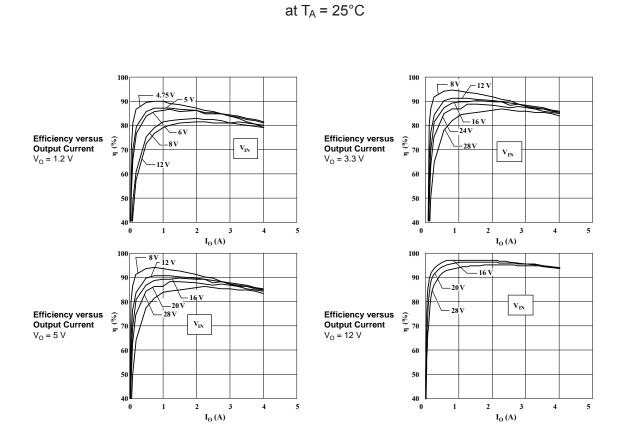

- High efficiency, 94% maximum at  $V_{IN} = 8 \text{ V}, V_O = 5 \text{ V},$ and  $I_O = 0.5 \text{ A}$

- Operating frequency 350 kHz, supports downsizing of smoothing choke coil

- Soft start and output on/off functions built-in

- Built-in protection:

- Drooping overcurrent protection

- Overtemperature protection

- Undervoltage lockout (UVLO)

# Package: 8-pin DIP

# Description

The SI-8105QL is a step-down switching regulator IC, designed as an output voltage regulator at the secondary stage of switch mode power supplies. The current-mode control system permits small ceramic capacitors to be used as output capacitors. Together with the compact DIP8 package, this allows reduction of regulator circuitry area on the PCB by approximately 50% in comparison with conventional topologies.

Designed to save power, losses in the SI-8105QL are reduced by controlling the maximum on-resistance of a built-in output MOSFET to as low as  $165 \text{ m}\Omega$ . Furthermore, die miniaturization has been accomplished through a proprietary BCD process.

The SI-8105QL supplies an output current of 3.5 A and an output voltage that is variable from 0.5 to 24 V, which is easily set to a voltage compatible with the diverse reduced power supply voltages required by signal processing ICs. Accepting a wide input voltage range, from 4.75 to 28 V, the SI-8105QL can be driven directly by a 24 V power supply.

Applications include power supplies for signal processing ICs for memories and microcomputers used in plasma display panel (PDP) TVs, liquid crystal display (LCD) TVs, computer hard drives, and DVD recorders.

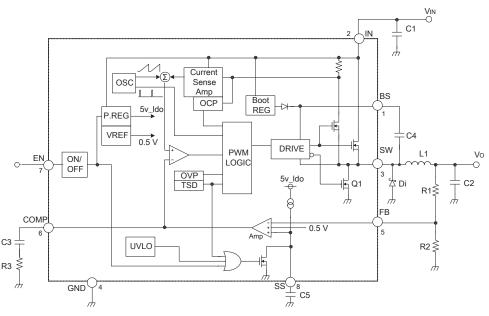

# **Functional Block Diagram**

### **Selection Guide**

| Part Number | Packing              |  |  |

|-------------|----------------------|--|--|

| SI8105QL-TL | 1000 pieces per reel |  |  |

### **Absolute Maximum Ratings**

| Characteristic                           | Symbol           | Remarks                                                                                                                        | Rating     | Unit |

|------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|------------|------|

| DC Input Voltage                         | V <sub>IN</sub>  |                                                                                                                                | 30         | V    |

| DC Input Voltage                         | V <sub>EN</sub>  |                                                                                                                                | 6          | V    |

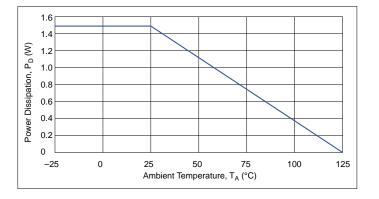

| Allowable Power Dissipation              | P <sub>D</sub>   | Limited by internal thermal shutdown, mounted on a 70 mm × 60 mm glass epoxy PCB with 1310 mm <sup>2</sup> exposed copper area | 1.50       | W    |

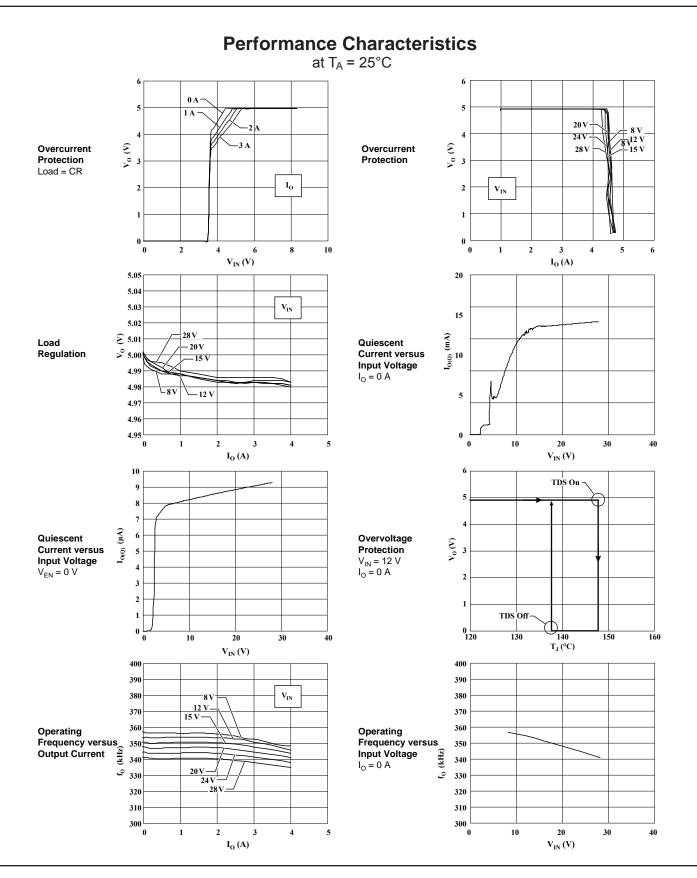

| Junction Temperature                     | TJ               | Internal thermal shutdown activates at approximately 140°C                                                                     | -30 to 150 | °C   |

| Storage Temperature                      | T <sub>stg</sub> |                                                                                                                                | -40 to 150 | °C   |

| Thermal Resistance (Junction to Ambient) | R <sub>θJA</sub> | Mounted on a 70 mm × 60 mm glass epoxy PCB with 1310 mm <sup>2</sup> exposed copper area                                       | 67         | °C/W |

| Thermal Resistance (Junction to Case)    | R <sub>θJC</sub> |                                                                                                                                | 25         | °C/W |

### **Recommended Operating Conditions\***

| Characteristic                          | Symbol           | Remarks                                                                                                                                                                                                       | Min.           | Тур. | Max. | Units |

|-----------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|------|-------|

| DC Input Voltage Range                  | V <sub>IN</sub>  | $V_{IN}(min)$ is the greater of either 4.75 V or V <sub>0</sub> +3 V; except if V <sub>0</sub> + 2 ≤ V <sub>IN</sub> ≤ V <sub>0</sub> + 3 V, then V <sub>IN</sub> (min) is set such that I <sub>0</sub> ≤ 2 A | See<br>remarks | -    | 28   | V     |

| DC Output Current Range                 | Ι <sub>Ο</sub>   | Using the circuit defined in the Typical Application diagram and within $P_D$ limits                                                                                                                          | 0              | _    | 3.5  | А     |

| Operating Junction<br>Temperature Range | T <sub>JOP</sub> |                                                                                                                                                                                                               | -30            | -    | 125  | °C    |

| Operating Temperature<br>Range          | T <sub>OP</sub>  | Operation within $P_D$ limits                                                                                                                                                                                 | -30            | _    | 85   | °C    |

\*Recommended operating range indicates conditions which are required for maintaining normal circuit functions shown in the Electrical Characteristics table.

| Characteristics                           | Symbol                      | Conditions                                                                               | Min   | Тур   | Max   | Units |

|-------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Reference Voltage                         | V <sub>REF</sub>            | V <sub>IN</sub> = 12 V, I <sub>O</sub> = 1.0 A                                           | 0.485 | 0.500 | 0.515 | V     |

| Output Voltage Temperature<br>Coefficient | $\Delta V_{REF} / \Delta T$ | $V_{IN}$ = 12 V, I <sub>O</sub> = 1.0 A, T <sub>A</sub> = -25°C to 100°C                 | -     | ±0.05 | _     | mV/°C |

| Efficiency <sup>2</sup>                   | η                           | V <sub>IN</sub> = 12 V, V <sub>O</sub> = 5 V, I <sub>O</sub> = 1 A                       | -     | 90    | _     | %     |

| Operating Frequency                       | f <sub>O</sub>              | V <sub>IN</sub> = 16 V, V <sub>O</sub> = 5 V, I <sub>O</sub> = 1 A                       | 315   | 350   | 385   | kHz   |

| Line Regulation                           | V <sub>LINE</sub>           | $V_{IN}$ = 8 to 28 V, $V_O$ = 5 V, $I_O$ = 1 A                                           | -     | 20    | 50    | mV    |

| Load Regulation                           | V <sub>LOAD</sub>           | $V_{IN}$ = 12 V, $V_{O}$ = 5 V, $I_{O}$ = 0.1 to 3.5 A                                   | -     | 20    | 50    | mV    |

| Overcurrent Protection Threshold          | Is                          | V <sub>IN</sub> = 12 V, V <sub>O</sub> = 5 V                                             | 3.6   | -     | 6.0   | A     |

| Quiescent Current 1                       | l <sub>iN</sub>             | $V_{IN}$ = 12 V, $V_{O}$ = 5 V, $I_{O}$ = 0 A, $V_{EN}$ = open                           | -     | 18    | _     | mA    |

| Quiescent Current 2                       | I <sub>IN(off)</sub>        | V <sub>IN</sub> = 12 V, V <sub>O</sub> = 5 V, I <sub>O</sub> = 0 A,V <sub>EN</sub> = 0 V | -     | -     | 20    | μA    |

| SS Terminal Leakage Current <sup>3</sup>  | I <sub>SSL</sub>            | V <sub>SSL</sub> = 0 V, V <sub>IN</sub> = 12 V                                           | -     | 5     | -     | μA    |

| EN Terminal High Level Voltage            | V <sub>CEH</sub>            | V <sub>IN</sub> = 12 V                                                                   | 2.8   | -     | -     | V     |

| EN Terminal Low Level Voltage             | V <sub>CEL</sub>            | V <sub>IN</sub> = 12 V                                                                   | -     | -     | 2.0   | V     |

| EN Terminal Leakage Current               | I <sub>CEH</sub>            | V <sub>EN</sub> = 0 V                                                                    | -     | 1     | _     | μA    |

| Error Amplifier Voltage Gain              | A <sub>EA</sub>             |                                                                                          | -     | 1000  | _     | V/V   |

| Error Amplifier Transconductance          | G <sub>EA</sub>             |                                                                                          | -     | 800   | _     | μA/V  |

| Current Sense To COMP<br>Transimpedance   | 1/G <sub>CS</sub>           |                                                                                          | -     | 0.35  | _     | V/A   |

| Maximum Duty Cycle (On)                   | DC <sub>MAX</sub>           |                                                                                          | -     | 92    | _     | %     |

| Minimum On-Time                           | t <sub>MIN</sub>            |                                                                                          | -     | 100   | _     | ns    |

<sup>1</sup>Using circuit shown in Measurement Circuit diagram.

<sup>2</sup>Efficiency is calculated as:  $\eta(\%) = ([V_O \times I_O] / [V_{IN} \times I_{IN}]) \times 100$ .

<sup>3</sup>SS terminal enables soft start when a an external capacitor is connected to it. Because a pull-up resistor is provided inside the IC, no external voltage can be applied to this terminal.

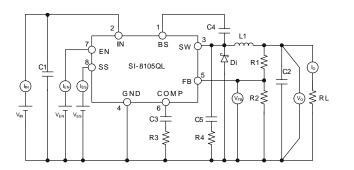

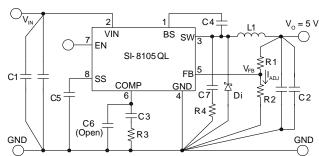

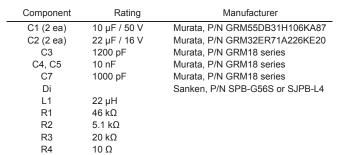

#### Measurement Circuit Diagram

| Component | Rating         |

|-----------|----------------|

| C1        | 10 µF / 50 V   |

| C2        | 47 µF / 25 V   |

| C3        | 1200 pF / 10 V |

| C4        | 10 nF / 25 V   |

| C5        | 1000 pF        |

| Di        | SPB-G56S       |

| L1        | 22 µH          |

| R1        | 46 kΩ          |

| R2        | 5.1 kΩ         |

| R3        | 20 kΩ          |

| R4        | 10 Ω           |

|           |                |

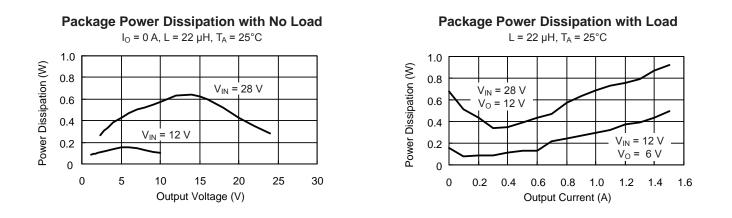

All performance characteristics given are typical values for circuit or system baseline design only and are at the nominal operating voltage and an ambient temperature,  $T_A$ , of 25°C, unless otherwise stated.

1310 mm<sup>2</sup> exposed copper area

Results calculated as:

1

$$P_{\rm D} = V_{\rm O} \times I_{\rm O} \left(\frac{100}{\eta x} - 1\right) - V_{\rm F} \times I_{\rm O} \left(1 - \frac{V_{\rm O}}{V_{\rm IN}}\right)$$

where:

Vo is the output voltage,

$V_{\text{IN}}$  is the Input voltage (0.4 V for these results),

$I_{O}$  is the Output current (0.3 A for these results),

$\eta x$  is the efficiency (%), which varies with  $V_{IN}$  and  $I_O$  (derived from the Efficiency curves in the Characteristic Performance section), and

$V_{\text{F}}$  is the diode forward voltage for D1, determination of the value for D1 should be made based on testing with the actual application (Sanken diode SFPB-54 was used for these results).

Note: When the SI-8105QL is operating in Discontinuous Conduction mode, the SI-8105QL has internal losses because the SI-8105QL must dissipate the energy from the charged Output capacitor (C2 in the Functional Block diagram) through the low-side switch MOSFET (Q1) on the SW circuit.

**Performance Characteristics**

27469.065, Rev. 1

SANKEN ELECTRIC CO., LTD.

**Diode Di** A Schottky-barrier diode must be used for Di. If other diode types, such as fast recovery diodes, are used, the IC may be destroyed because of reverse voltages applied by the recovery voltage or turn-on voltage.

**Choke Coil L1** If the winding resistance of the choke coil is too high, IC efficiency may go down to the extent that the resistance is beyond the rating. Because the overcurrent protection threshold current is approximately 4 A, attention must be paid to the heating of the choke coil by magnetic saturation due to overload or short-circulated load.

**Capacitors C1, C2, C3 and C7** Because large ripple currents for SMPS flow across C1 and C2, capacitors with high frequency and low impedance must be used. Especially when the impedance of C2 is high, the switching waveform may not be normal at low temperatures.

C3 is used to enable soft start. If the soft start function is not used, leave the SS terminal open.

C7 is for ringing noise suppression

**Resistors R1, R2 and R4** R1 and R2 set the output voltage,  $V_0$ . Select the resistor values to set  $I_{ADJ}$  to 0.1 mA.  $R_1$  and  $R_2$  are calculated by the following expression:

$$R_{1} = \frac{(V_{0} - V_{FB})}{I_{ADJ}} = \frac{(V_{0} - 0.5)}{1 \times 10^{-3}} (\Omega) \text{, and } R_{2} = \frac{V_{FB}}{I_{ADJ}} = \frac{0.5}{1 \times 10^{-3}} \cong 5 (k\Omega) \quad (1)$$

R4 is for ringing noise suppression.

For optimum performance, minimize the distance between components.

#### **Typical Application Diagram**

Note: If the value of output capacitor (C2) is large, or if it has a high ESR, or both, then C6 is required.

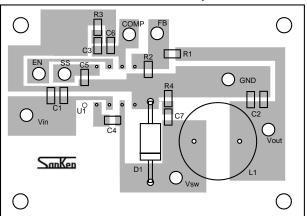

Recommended PCB Layout

All external components should be mounted as closely as possible to the SI-8105QL. The ground of all components should be connected at one point.

**Phase Compensation Components C3, C6, and R3** The stability and response of the loop is controlled through the COMP pin. The COMP pin is the output of the internal transconductance amplifier. The combination of a series-connected capacitor and resistor sets the combination of a pole and zero frequency point that decide the characteristics of the control system. The DC gain of the voltage feedback loop is calculated by the following equation:

$$Adc = Rl \times Gcs \times AEA \times \frac{VFB}{Vout} , \qquad (2)$$

where

$V_{FB}$  is the feedback voltage (0.5 V),

$A_{\text{EA}}$  is the error amplifier voltage gain,

G<sub>CS</sub> is the current sense transconductance, and

Rl is the load resistor value.

The system has two important poles. One is set by the phase compensation capacitor (C3) and the output resistor of the error amplifier. The other is set by the output capacitor and load resistor. These poles are calculated by the following equations:

$$fp1 = \frac{GEA}{2\pi \times C3 \times AEA} \quad , \tag{3}$$

$$fp2 = \frac{1}{2\pi \times C2 \times Rl} \quad , \tag{4}$$

where G<sub>EA</sub> is the error amplifier transconductance.

The system has one important zero. This is set by the phase compensation capacitor (C3) and phase compensation resistor (R3). The zero is shown by the following equation:

$$fz1 = \frac{1}{2\pi \times C3 \times R3} \tag{5}$$

If the value of the output capacitor is the large or if it has a high ESR, the system may have another important zero. This zero would be set by the ESR and capacitance of the output capacitor. The zero is shown by the following equation:

$$fESR = \frac{1}{2\pi \times C2 \times RESR} \quad . \tag{6}$$

In this case a third pole, which is set by the phase compensation capacitor (C6) and phase compensation resistor (R3), is used to compensate the effect of the ESR zero on the loop gain.

The pole is shown by the following equation:

$$fp3 = \frac{1}{2\pi \times C6 \times R3} \quad . \tag{7}$$

The goal of phase compensation design is to shape the converter transfer function to get the required loop gain. The system crossover frequency, where the feedback loop has unity gain, is important. Lower crossover frequencies result in slower line and load transient responses. On the other hand, higher crossover frequencies cause system instability. A good standard is to adjust the crossover frequency to approximately one-tenth of the switching frequency.

The optimal selection of phase compensation components can be determined using the following procedure:

1. Choose the phase compensation resistor (R3) to adjust the required crossover frequency. R3 value is calculated by the following equation:

$$R3 = \frac{2\pi \times C2 \times fc}{GEA \times GCS} \times \frac{Vout}{VFB} < \frac{2\pi \times C2 \times 0.1 \times fs}{GEA \times GCS} \times \frac{Vout}{VFB} \quad , \quad (8)$$

where  $f_c$  is the required crossover frequency. This is usually adjusted to less than one-tenth of the switching frequency.

2. Choose the phase compensation capacitor (C3) to get the required phase margin. For applications that have typical inductor values, adjusting the compensation zero to less than one-quarter of crossover frequency provides sufficient phase margin. The value of C3 is calculated by the following equation:

$$C3 > \frac{4}{2\pi \times R3 \times fc} \quad , \tag{9}$$

where R3 is the phase compensation resistor.

3. It is necessary to determine whether a second compensation capacitor (C6) is required. It is required if the ESR zero of the output capacitor is less than half of the switching frequency, expressed as follows:

$$\frac{1}{2\pi \times C2 \times RESR} < \frac{fs}{2} \quad . \tag{10}$$

If this is the case, add the second compensation capacitor (C6) and adjust ESR zero frequency  $(f_{p3})$ . C6 value is calculated by the following equation:

$$C6 = \frac{C2 \times RESR}{R3} \quad . \tag{11}$$

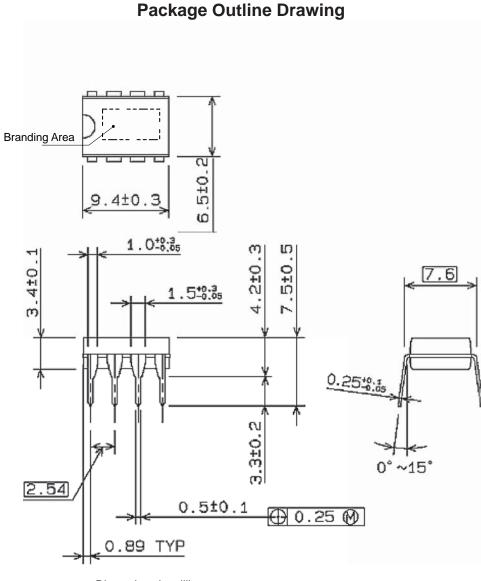

Dimensions in millimeters

Branding codes (exact appearance at manufacturer discretion): 1st line, type: 8105QL 2nd line, lot: YMW Where: Y is the last digit of the year of manufacture M is the month (1 to 9, O, N, D) W is the week of the month (1 to 5) 3rd line, control number: NNNN

$(\mathbb{P}_{0})$

Leadframe plating Pb-free. Device composition complies with the RoHS directive.

## Cautions

In general, the junction temperature level of surface mount package ICs is dependent upon the area and material of the PC board and its copper area. Therefore, please design the PCB to allow sufficient margin for heat dissipation.

**Parallel Operation** Parallel operation of multiple products to increase the current is not allowed.

**Thermal Shutdown** The SI-8000Q series has a thermal protection circuit. This circuit keeps the IC from the damage by overload. But this circuit cannot guarantee the long-term reliability against the continuous overload conditions.

**ESD Susceptibility** Take precautions against damage by static electricity.

- The contents in this document are subject to changes, for improvement and other purposes, without notice. Make sure that this is the latest revision of the document before use.

- Application and operation examples described in this document are quoted for the sole purpose of reference for the use of the products herein and Sanken can assume no responsibility for any infringement of industrial property rights, intellectual property rights or any other rights of Sanken or any third party which may result from its use.

- Although Sanken undertakes to enhance the quality and reliability of its products, the occurrence of failure and defect of semiconductor products at a certain rate is inevitable. Users of Sanken products are requested to take, at their own risk, preventative measures including safety design of the equipment or systems against any possible injury, death, fires or damages to the society due to device failure or malfunction.

- Sanken products listed in this document are designed and intended for the use as components in general purpose electronic equipment or apparatus (home appliances, office equipment, telecommunication equipment, measuring equipment, etc.).

When considering the use of Sanken products in the applications where higher reliability is required (transportation equipment and its control systems, traffic signal control systems or equipment, fire/crime alarm systems, various safety devices, etc.), and whenever long life expectancy is required even in general purpose electronic equipment or apparatus, please contact your nearest Sanken sales representative to discuss, prior to the use of the products herein.

The use of Sanken products without the written consent of Sanken in the applications where extremely high reliability is required (aerospace equipment, nuclear power control systems, life support systems, etc.) is strictly prohibited.

• In the case that you use Sanken products or design your products by using Sanken products, the reliability largely depends on the degree of derating to be made to the rated values. Derating may be interpreted as a case that an operation range is set by derating the load from each rated value or surge voltage or noise is considered for derating in order to assure or improve the reliability. In general, derating factors include electric stresses such as electric voltage, electric current, electric power etc., environmental stresses such as ambient temperature, humidity etc. and thermal stress caused due to self-heating of semiconductor products. For these stresses, instantaneous values, maximum values and minimum values must be taken into consideration.

In addition, it should be noted that since power devices or IC's including power devices have large self-heating value, the degree of derating of junction temperature affects the reliability significantly.

- When using the products specified herein by either (i) combining other products or materials therewith or (ii) physically, chemically or otherwise processing or treating the products, please duly consider all possible risks that may result from all such uses in advance and proceed therewith at your own responsibility.

- Anti radioactive ray design is not considered for the products listed herein.

- Sanken assumes no responsibility for any troubles, such as dropping products caused during transportation out of Sanken's distribution network.

- The contents in this document must not be transcribed or copied without Sanken's written consent.