**TOSHIBA Intelligent Power Module**

# **MIG20J503L**

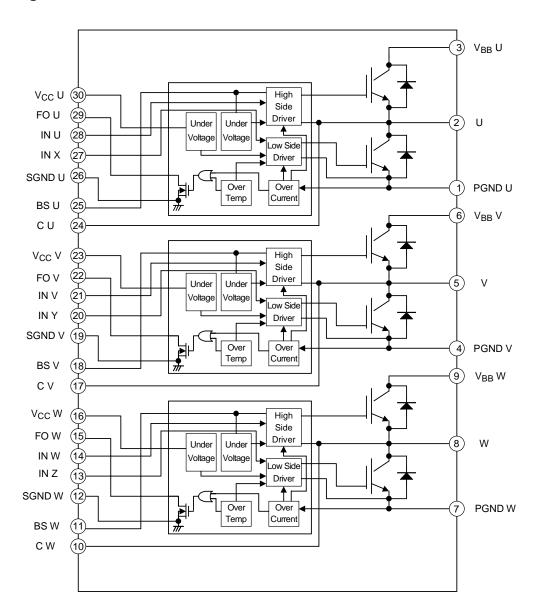

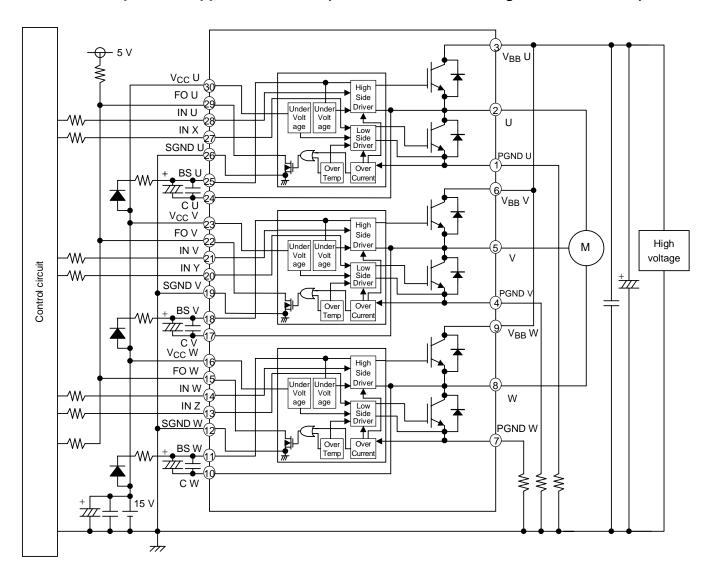

MIG20J503L is an intelligent power module for three-phase inverter system. The 4th generation low saturation voltage trench gate IGBT and FRD are connected to a three-phase full bridge type, and IC by the original high-voltage SOI (silicon-on-insulator) process drives these directly in response to a PWM signal. Moreover, since high-voltage level-shifter is built in high-voltage IC, while being able to perform a direct drive without the interface with which the upper arm IGBT is insulated, the drive power supply of an upper arm can be driven with a bootstrap system, and the simplification of a system is possible. Furthermore, each lower arm emitter terminal has been independent so that detection can perform current detection at

Weight: 18 g (typ.)

the time of vector control by current detection resistance of a lower arm. The protection function builds in Under Voltage Protection, Short Circuit Protection for a low arm IGBT, and Over Temperature Protection. Original high thermal conduction resin is adopted as a package, and low heat resistance is realized.

#### **Features**

- The 4th generation trench gate thin wafer NPT IGBT is adopted.

- FRD is built in.

- The level shift circuit by high-voltage IC is built in.

- The simplification of a high side driver power supply is possible by the bootstrap system.

- Short circuit protection for a low arm IGBT, over temperature protection, and the power supply under voltage protection function are built in.

- Short circuit protection for a low arm IGBT and over temperature protection state are outputted.

- The lower arm emitter terminal has been independent by each phase for the purpose of the current detection at the time of vector control.

- Low thermal resistance by adoption of original high thermal conduction resin.

Since this product is MOS structure, it should be careful of static electricity in the case of handling.

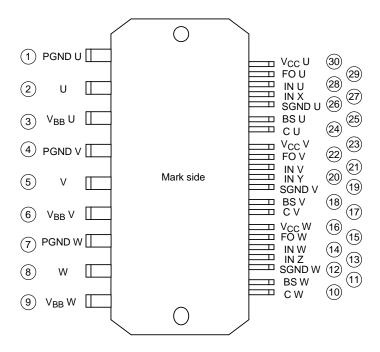

### **Pin Assignment**

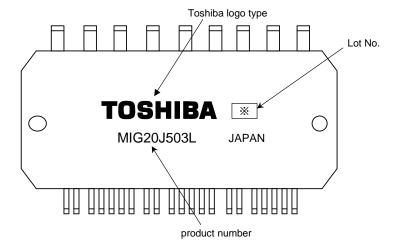

## Marking

### **Block Diagram**

## **Pin Description**

| Pin No. | Symbol            | Pin Description                                                                                                                      |  |  |

|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | PGND U            | U-Phase Power Ground pin (connect a current detecting resistor between this pin and SGND U pin)                                      |  |  |

| 2       | U                 | U-Phase output pin                                                                                                                   |  |  |

| 3       | V <sub>BB</sub> U | U-Phase high-voltage power supply pin                                                                                                |  |  |

| 4       | PGND V            | V-Phase Power Ground pin (connect a current detecting resistor between this pin and SGND V pin)                                      |  |  |

| 5       | V                 | -Phase output pin                                                                                                                    |  |  |

| 6       | V <sub>BB</sub> V | V-Phase high-voltage power supply pin                                                                                                |  |  |

| 7       | PGND W            | W-Phase Power Ground pin (connect a current detecting resistor between this pin and SGND W pin)                                      |  |  |

| 8       | W                 | W-Phase output pin                                                                                                                   |  |  |

| 9       | V <sub>BB</sub> W | W-Phase high-voltage power supply pin                                                                                                |  |  |

| 10      | C W               | W-Phase bootstrap capacitor connecting pin (–)                                                                                       |  |  |

| 11      | BS W              | W-Phase bootstrap capacitor connecting pin (+)                                                                                       |  |  |

| 12      | SGND W            | W-Phase Signal Ground pin                                                                                                            |  |  |

| 13      | IN Z              | W-Phase low-side input pin (negative logic)                                                                                          |  |  |

| 14      | IN W              | W-Phase high-side input pin (negative logic)                                                                                         |  |  |

| 15      | FO W              | W-Phase Diagnosis output pin (open drain output. Wired or connection can be performed with the diagnosis output pin of other phase.) |  |  |

| 16      | V <sub>CC</sub> W | W-Phase control power supply (+15 V typ.)                                                                                            |  |  |

| 17      | CV                | V-Phase bootstrap capacitor connecting pin (-)                                                                                       |  |  |

| 18      | BS V              | V-Phase bootstrap capacitor connecting pin (+)                                                                                       |  |  |

| 19      | SGND V            | V-Phase Signal Ground pin                                                                                                            |  |  |

| 20      | IN Y              | V-Phase low-side input pin (negative logic)                                                                                          |  |  |

| 21      | IN V              | V-Phase high-side input pin (negative logic)                                                                                         |  |  |

| 22      | FO V              | V-Phase Diagnosis output pin (open drain output. Wired or connection can be performed with the diagnosis output pin of other phase.) |  |  |

| 23      | V <sub>CC</sub> V | V-Phase control power supply (+15 V typ.)                                                                                            |  |  |

| 24      | CU                | U-Phase bootstrap capacitor connecting pin (–)                                                                                       |  |  |

| 25      | BS U              | U-Phase bootstrap capacitor connecting pin (+)                                                                                       |  |  |

| 26      | SGND U            | U-Phase Signal Ground pin                                                                                                            |  |  |

| 27      | IN X              | U-Phase low-side input pin (negative logic)                                                                                          |  |  |

| 28      | IN U              | U-Phase high-side input pin (negative logic)                                                                                         |  |  |

| 29      | FO U              | U-Phase Diagnosis output pin (open drain output. Wired or connection can be performed with the diagnosis output pin of other phase.) |  |  |

| 30      | V <sub>CC</sub> U | U-Phase control power supply (+15 V typ.)                                                                                            |  |  |

#### **Truth Table**

| Protection Circuit Detection State |                              |               | Input               |                         | IGBT State             |                  | Fault Output    |        |

|------------------------------------|------------------------------|---------------|---------------------|-------------------------|------------------------|------------------|-----------------|--------|

| High Side<br>Under<br>Voltage      | Low Side<br>Under<br>Voltage | Short Circuit | Over<br>Temperature | IN (X) High<br>Side Arm | IN (X) Low<br>Side Arm | High Side<br>Arm | Low Side<br>Arm | FO (X) |

| Un-Detecting                       | Un-Detecting                 | Un-Detecting  | Un-Detecting        | н                       | Н                      | OFF              | OFF             | OFF    |

| Un-Detecting                       | Un-Detecting                 | Un-Detecting  | Un-Detecting        | Н                       | L                      | OFF              | ON              | OFF    |

| Un-Detecting                       | Un-Detecting                 | Un-Detecting  | Un-Detecting        | L                       | Н                      | ON               | OFF             | OFF    |

| Un-Detecting                       | Un-Detecting                 | Un-Detecting  | Un-Detecting        | L                       | L                      | OFF              | OFF             | OFF    |

| Detecting                          | Un-Detecting                 | Un-Detecting  | Un-Detecting        | Н                       | Н                      | OFF              | OFF             | OFF    |

| Detecting                          | Un-Detecting                 | Un-Detecting  | Un-Detecting        | Н                       | L                      | OFF              | ON              | OFF    |

| Detecting                          | Un-Detecting                 | Un-Detecting  | Un-Detecting        | L                       | Н                      | OFF              | OFF             | OFF    |

| Detecting                          | Un-Detecting                 | Un-Detecting  | Un-Detecting        | L                       | L                      | OFF              | OFF             | OFF    |

| Un-Detecting                       | Detecting                    | Un-Detecting  | Un-Detecting        | Н                       | Н                      | OFF              | OFF             | OFF    |

| Un-Detecting                       | Detecting                    | Un-Detecting  | Un-Detecting        | Н                       | L                      | OFF              | OFF             | OFF    |

| Un-Detecting                       | Detecting                    | Un-Detecting  | Un-Detecting        | L                       | Н                      | OFF              | OFF             | OFF    |

| Un-Detecting                       | Detecting                    | Un-Detecting  | Un-Detecting        | L                       | L                      | OFF              | OFF             | OFF    |

| Detecting                          | Detecting                    | Un-Detecting  | Un-Detecting        | Н                       | Н                      | OFF              | OFF             | OFF    |

| Detecting                          | Detecting                    | Un-Detecting  | Un-Detecting        | Н                       | L                      | OFF              | OFF             | OFF    |

| Detecting                          | Detecting                    | Un-Detecting  | Un-Detecting        | L                       | Н                      | OFF              | OFF             | OFF    |

| Detecting                          | Detecting                    | Un-Detecting  | Un-Detecting        | L                       | L                      | OFF              | OFF             | OFF    |

| Un-Detecting                       | Un-Detecting                 | Detecting     | Un-Detecting        | Н                       | Н                      | OFF              | OFF             | ON     |

| Un-Detecting                       | Un-Detecting                 | Detecting     | Un-Detecting        | Н                       | L                      | OFF              | OFF             | ON     |

| Un-Detecting                       | Un-Detecting                 | Detecting     | Un-Detecting        | L                       | Н                      | OFF              | OFF             | ON     |

| Un-Detecting                       | Un-Detecting                 | Detecting     | Un-Detecting        | L                       | L                      | OFF              | OFF             | ON     |

| Un-Detecting                       | Un-Detecting                 | Un-Detecting  | Detecting           | Н                       | Н                      | OFF              | OFF             | ON     |

| Un-Detecting                       | Un-Detecting                 | Un-Detecting  | Detecting           | Н                       | L                      | OFF              | OFF             | ON     |

| Un-Detecting                       | Un-Detecting                 | Un-Detecting  | Detecting           | L                       | Н                      | OFF              | OFF             | ON     |

| Un-Detecting                       | Un-Detecting                 | Un-Detecting  | Detecting           | L                       | L                      | OFF              | OFF             | ON     |

| Un-Detecting                       | Un-Detecting                 | Detecting     | Detecting           | Н                       | Н                      | OFF              | OFF             | ON     |

| Un-Detecting                       | Un-Detecting                 | Detecting     | Detecting           | Н                       | L                      | OFF              | OFF             | ON     |

| Un-Detecting                       | Un-Detecting                 | Detecting     | Detecting           | L                       | Н                      | OFF              | OFF             | ON     |

| Un-Detecting                       | Un-Detecting                 | Detecting     | Detecting           | L                       | L                      | OFF              | OFF             | ON     |

- · The above has indicated a part for single arm.

- There is no relevance of operation between arms.

- When the input of a high side arm and a low side arm is simultaneously set to "L", IGBT of a high side arm and a low side arm turns off.

- FO (X) terminal is turned on in the meantime at the same time, as for the output of Phase which detected the load short circuit state, it will maintain the OFF between 10 ms, if a Short Current Protection detects a Short Current state for a low arm IGBT. Although an incoming signal is reset by an upper arm and a lower arm being simultaneously set to "H" in the back in this state, OFF of an output and FO (X) are maintained between 10 ms. Although FO (X) is turned off when FO (X) terminal for 10 ms will not be in the simultaneous "H" state of an upper arm and a lower arm in during ON time, an output maintains OFF. This release is made by an upper arm and a lower arm being simultaneously set to "H".

- (Short current protection is a non-repetition. When FO (X) turns on, please turn off the input of all phase.)

- If an Over Temperature Protection circuit detects an Over Temperature state, while the output of Phase which detected the Over Temperature Protection state is turned off, FO (X) terminal turns it on. This state will return operation, if temperature falls to Over Temperature Protection detection return temperature (over temperature protection temperature over temperature protection hysteresis).

# Absolute Maximum Rating ( $T_j = 25$ °C)

| Characteristics               | Symbol                  | Rating          | Unit   |  |

|-------------------------------|-------------------------|-----------------|--------|--|

|                               | $V_{BB}$                | 450             |        |  |

| Power supply voltage          | V <sub>BB</sub> (surge) | 500             | V      |  |

| Tower supply vollage          | V <sub>CC</sub>         | 20              |        |  |

|                               | V <sub>BS</sub>         | 20              |        |  |

| Collector-emitter voltage     | V <sub>CES</sub>        | 600             | V      |  |

| Each collector current (DC)   | Ic                      | ±20             | Α      |  |

| Each collector current (PEAK) | I <sub>CP</sub>         | ±40             | Α      |  |

| Input voltage                 | V <sub>IN</sub>         | 5.5             | V      |  |

| Fault output supply voltage   | V <sub>FO</sub>         | 20              | V      |  |

| Fault output current          | I <sub>FO</sub>         | 15              | mA     |  |

| PGND-SGND voltage difference  | V <sub>PGND-SGND</sub>  | ±5              | V      |  |

| Output voltage rate of change | dv/dt                   | 20              | kV/μs  |  |

| Collector power dissipation   | P <sub>C</sub>          | 43              | W      |  |

| (per 1 IGBT chip) (Tc = 25°C) | FC                      | 43              | VV     |  |

| Collector power dissipation   | P <sub>C</sub>          | 25              | W      |  |

| (per 1 FRD chip) (Tc = 25°C)  | r C                     | 25              | VV     |  |

| Operating temperature         | T <sub>OPE</sub>        | -20 to 100      | °C     |  |

| Junction temperature (Note 1) | Tj                      | 150             | °C     |  |

| Storage temperature           | T <sub>stg</sub>        | -40 to 125      | °C     |  |

| Isolation voltage             | V <sub>ISO</sub>        | 2500 (1 min)    | Vrms   |  |

| (60 Hz sinusoidal, AC)        | VISO                    | 2300 (1 111111) | VIIIIS |  |

| Screw torque (M3)             |                         | 0.5             | N∙m    |  |

Note 1: Although a junction temperature is 150°C the own maximum moment of a power chips which it builds in this module, the average operation junction temperature for carrying out safe operation specifies it as 125°C or less.

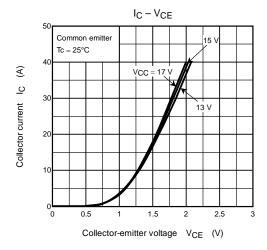

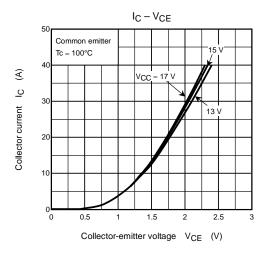

## Electrical Characteristics ( $T_j = 25^{\circ}C$ )

| Characteristics                                                  | Symbol                | Test Condition                                                                                                                                                                   | Min   | Тур. | Max  | Unit    |  |

|------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|---------|--|

|                                                                  | $V_{BB}$              |                                                                                                                                                                                  |       | 300  | 400  | V       |  |

| Operating power supply voltage                                   | V <sub>CC</sub>       |                                                                                                                                                                                  |       | 15   | 17   |         |  |

|                                                                  | V <sub>BS</sub>       | _                                                                                                                                                                                | 13.5  | 15   | 17   | <u></u> |  |

|                                                                  | I <sub>BB</sub>       | V <sub>BB</sub> = 400 V, V <sub>IN</sub> = 5 V (1 arm)                                                                                                                           | _     | _    | 1    |         |  |

|                                                                  | Icc                   | V <sub>CC</sub> = 15 V, V <sub>IN</sub> = 5 V (1 arm)                                                                                                                            |       | 0.8  | 1.5  | mA      |  |

| Current dissipation                                              |                       | V <sub>CC</sub> = 15 V, V <sub>IN</sub> = 0 V (1 arm)                                                                                                                            | _     | 1.1  | 1.5  |         |  |

|                                                                  | I                     | V <sub>CC</sub> = 15 V, V <sub>IN</sub> = 5 V (1 arm)                                                                                                                            | _     | 330  | 600  | μА      |  |

|                                                                  | I <sub>BS</sub>       | V <sub>CC</sub> = 15 V, V <sub>IN</sub> = 0 V (1 arm)                                                                                                                            | _     | 470  | 1000 |         |  |

| Input voltage                                                    | V <sub>IH</sub>       | V <sub>IN</sub> = "H"                                                                                                                                                            | 3.5   | 2.8  | _    | V       |  |

| Input voltage                                                    | V <sub>IL</sub>       | V <sub>IN</sub> = "L"                                                                                                                                                            | _     | 2.3  | 1.5  |         |  |

| Input voltage historogie                                         | .,                    | V <sub>IN</sub> = "H" → "L"                                                                                                                                                      | _     | 0.5  | _    | .,      |  |

| Input voltage histeresis                                         | $V_{INhys}$           | V <sub>IN</sub> = "L" → "H"                                                                                                                                                      | _     | 0.5  | _    | V       |  |

| Input current                                                    | I <sub>IH</sub>       | V <sub>CC</sub> = 15 V, V <sub>IN</sub> = 5 V                                                                                                                                    | 0     | 5    | 30   | ^       |  |

| Input current                                                    | I <sub>IL</sub>       | V <sub>CC</sub> = 15 V, V <sub>IN</sub> = 0 V                                                                                                                                    | 15    | 30   | 60   | μА      |  |

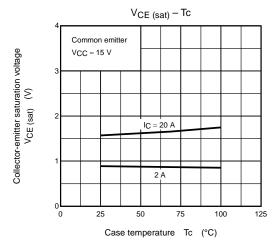

| IGBT saturation voltage                                          | V <sub>sat</sub> U    | $V_{CC} = 15 \text{ V}, V_{BS} = 15 \text{ V}, I_{C} = 20 \text{ A},$ upper arm                                                                                                  | — 1.6 |      | 2.1  | V       |  |

|                                                                  | V <sub>sat</sub> L    | $V_{CC} = 15 \text{ V}, I_C = 20 \text{ A}, \text{ lower arm}$                                                                                                                   | _     | 1.6  | 2.1  |         |  |

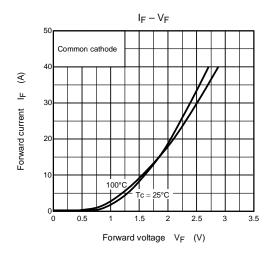

| FRD forward voltage                                              | V <sub>F</sub> U      | I <sub>F</sub> = 20 A, upper arm                                                                                                                                                 | _     | 2.0  | 2.7  | V       |  |

| TRD forward voltage                                              | V <sub>F</sub> L      | I <sub>F</sub> = 20 A, lower arm                                                                                                                                                 | _     | 2.0  | 2.7  | •       |  |

| Fault output voltage                                             | V <sub>FO</sub>       | I <sub>FO</sub> = 5 mA                                                                                                                                                           | _     | 0.8  | 1.2  | V       |  |

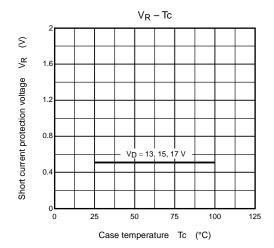

| Short current protection voltage                                 | V <sub>R</sub>        | Short current protection (Note 2)                                                                                                                                                | 0.45  | 0.5  | 0.55 | V       |  |

| Short current protection delay time                              | V <sub>R t d</sub>    | Short current protection                                                                                                                                                         | 1.0   | 1.5  | 2.0  | μS      |  |

| Fault output pulse width                                         | V <sub>R t h</sub>    | Short current protection                                                                                                                                                         | _     | 10   | _    | ms      |  |

| Over temperature protection                                      | TSD                   | Over temperature protection                                                                                                                                                      | 150   | 165  | 200  | °C      |  |

| Over temperature protection hys.                                 | ΔTSD                  | Over temperature protection return                                                                                                                                               | _     | 20   | _    | °C      |  |

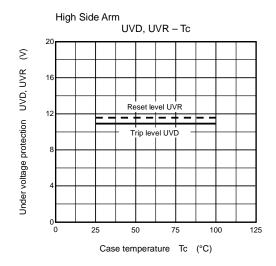

| Under voltage protection                                         | V <sub>BS</sub> UVD   | Upper arm under voltage protection                                                                                                                                               | 10.0  | 11.0 | 12.0 | V       |  |

| Under voltage protection recovery                                | V <sub>BS</sub> UVR   | Upper arm under voltage protection recovery                                                                                                                                      | 10.5  | 11.5 | 12.5 | V       |  |

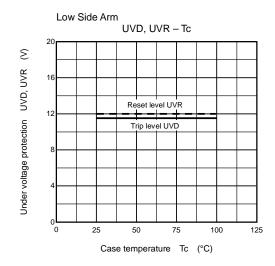

| Under voltage protection                                         | $V_{CC}UVD$           | Lower arm under voltage protection                                                                                                                                               | 10.5  | 11.5 | 12.5 | V       |  |

| Under voltage protection recovery                                | V <sub>CC</sub> UVR   | Lower arm under voltage protection recovery                                                                                                                                      | 11.0  | 12.0 | 13.0 | V       |  |

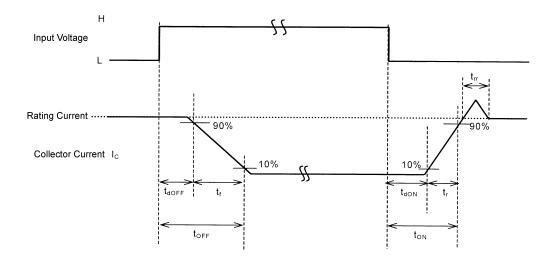

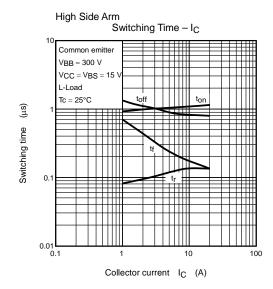

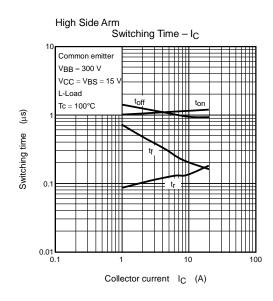

| IGBT turn-on propagation delay time                              | t <sub>dON</sub>      |                                                                                                                                                                                  | 1     | 0.8  | _    | μS      |  |

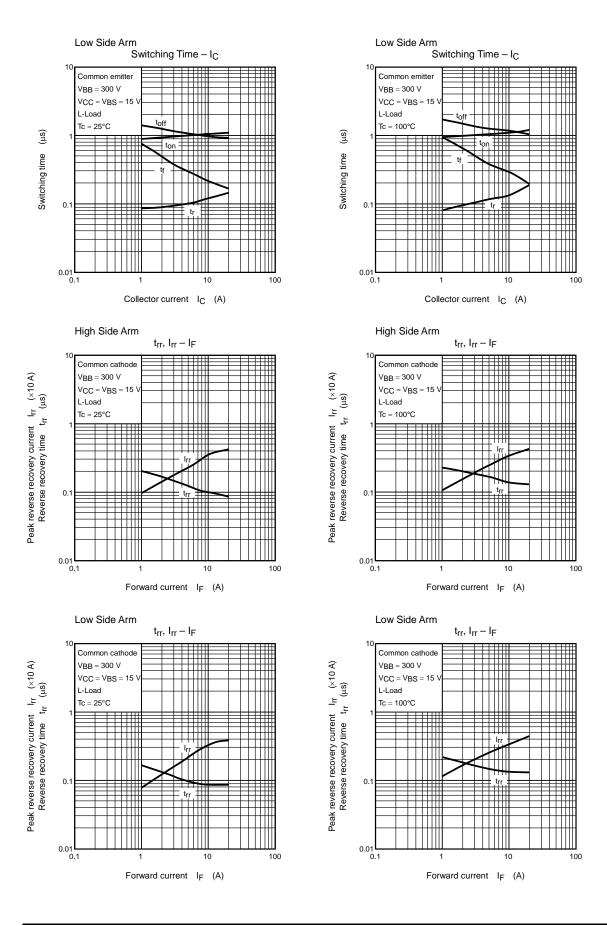

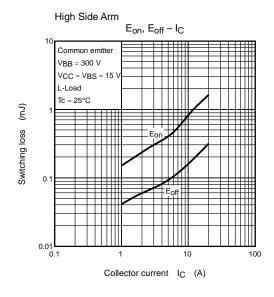

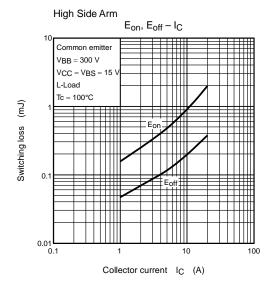

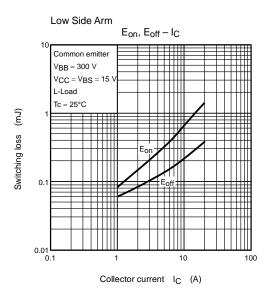

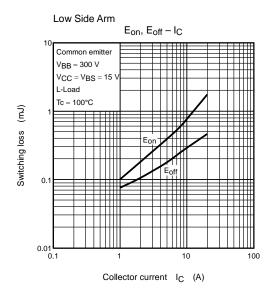

| IGBT rise time                                                   | t <sub>r</sub>        | V <sub>BB</sub> = 300 V,                                                                                                                                                         |       | 0.16 | 0.4  | μS      |  |

| IGBT turn-on time                                                | ton                   | $V_{CC} = 15 \text{ V}.$                                                                                                                                                         |       | 1.0  | 1.6  | μS      |  |

| IGBT turn-off propagation delay time                             | t <sub>dOFF</sub>     | V <sub>BS</sub> = 15 V,<br>I <sub>C</sub> = 20 A,<br>Inductive load (Note 3)                                                                                                     |       | 0.7  | _    | μS      |  |

| IGBT fall time                                                   | t <sub>f</sub>        | inductive load (Note 3)                                                                                                                                                          |       | 0.16 | 0.4  | μS      |  |

| IGBT turn-off time                                               | toff                  |                                                                                                                                                                                  | _     | 0.9  | 1.3  | μS      |  |

| IGBT vertical arm turn-on, a turn-off propagation delay time lag | t <sub>ONH</sub>      | $V_{BB} = 300 \text{ V}, V_{CC} = 15 \text{ V}, V_{BS} = 15 \text{ V}, I_{C} = 20 \text{ A, inductive load}$ (include each phase)                                                |       | 0    | 300  | ns      |  |

| IGBT vertical arm turn-on, a turn-off propagation delay time lag | t <sub>OFFL</sub> -   | $\begin{aligned} V_{BB} &= 300 \text{ V, } V_{CC} = 15 \text{ V, } V_{BS} = 15 \text{ V,} \\ I_{C} &= 20 \text{ A, inductive load} \\ \text{(include each phase)} \end{aligned}$ | _     | 0    | 300  | ns      |  |

| Daed time                                                        | t <sub>dead</sub>     | $\begin{aligned} V_{BB} &= 300 \text{ V}, \text{ V}_{CC} = 15 \text{ V}, \text{ V}_{BS} = 15 \text{ V}, \\ I_{C} &= 20 \text{ A, inductive load} \end{aligned}$                  | 1     | _    | _    | μS      |  |

| FRD reverse recovery time                                        | t <sub>rr</sub>       | $\begin{array}{c} V_{BB} = 300 \text{ V}, \text{ V}_{CC} = 15 \text{ V}, \text{ V}_{BS} = 15 \text{ V}, \\ I_F = 20 \text{ A} & \text{(Note 3)} \end{array}$                     | _     | 100  | _    | ns      |  |

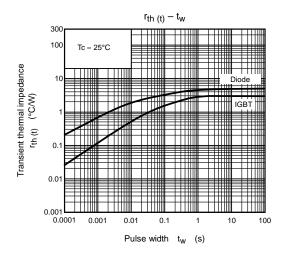

| Thermal resistance                                               | R <sub>th (j-c)</sub> | Transistor stage                                                                                                                                                                 | _     | _    | 2.9  | °C/W    |  |

| o.mai rosistanoe                                                 |                       | Diode stage                                                                                                                                                                      | _     | —    | 5.0  | 0, 00   |  |

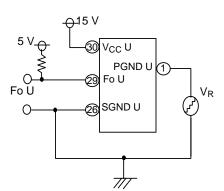

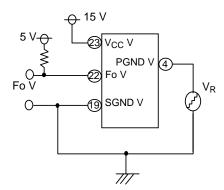

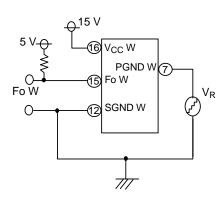

Note 2: V<sub>R</sub> measurement circuit

**U-Phase**

V-Phase

W-Phase

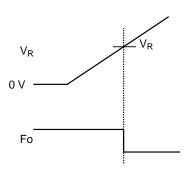

**Timing Chart**

$\ensuremath{V_R}$  is measured by giving the sweep voltage from the outside like the above-mentioned.

When the overcurrent detection value is set by an actual application, it is necessary to consider the resistance of the internal bonding wire.

The resistance of the internal bonding wire is 5.5 m $\Omega$ .

Note 3: Switching waveform

8

## The Example of an Application Circuit (in the case of not insulating with a control side)

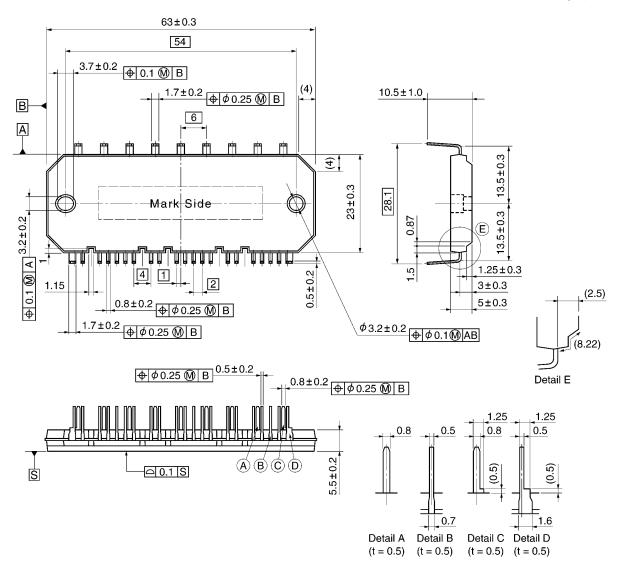

## Package Dimensions: TOSHIBA 2-63A1A

Unit: mm

Weight: 18 g (typ.)

### **RESTRICTIONS ON PRODUCT USE**

030619EBA

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of

safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of

such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.