# Contents

| Page | Section | Title                                                                                  |

|------|---------|----------------------------------------------------------------------------------------|

| 3    | 1.      | Introduction                                                                           |

| 3    | 1.1.    | General Description                                                                    |

| 3    | 1.2.    | Environment                                                                            |

| 5    | 2.      | Specifications                                                                         |

| 5    | 2.1.    | Outline Dimensions                                                                     |

| 5    | 2.2.    | Pin Connections                                                                        |

| 5    | 2.2.1.  | 40-Pin Dil Package                                                                     |

| 6    | 2.2.2.  | 44-Pin PLCC Package                                                                    |

| 7    | 2.3.    | Pin Descriptions                                                                       |

| 8    | 2.4.    | Pin Circuits                                                                           |

| 10   | 2.5.    | Electrical Characteristics                                                             |

| 10   | 2.5.1.  | Absolute Maximum Ratings                                                               |

| 11   | 2.5.2.  | Recommended Operating Conditions                                                       |

| 12   | 2.5.3.  | Characteristics                                                                        |

| 18   | 3.      | Functional Description                                                                 |

| 18   | 3.1.    | Block Diagram                                                                          |

| 18   | 3.2.    | The Video Clamping Circuit and the Sync Pulse Separation Circuit                       |

| 19   | 3.3.    | Horizontal Synchronization                                                             |

| 19   | 3.3.1.  | Non-Color-Locked Operation                                                             |

| 20   | 3.3.2.  | Color-Locked Operation                                                                 |

| 21   | 3.3.3.  | Skew Data Output and Field Number Information                                          |

| 2.6  | 3.3.4.  | Synchronism Detector for PLL and Muting Signal                                         |

| 27   | 3.4.    | Start Oscillator and Protection Circuit                                                |

| 28   | 3.5.    | Blanking and Color Key Pulses                                                          |

| 28   | 3.6.    | Output for Switching the Horizontal Power Stage Between 15.6 kHz (PAL/NTSC) and 18 kHz |

|      |         | (Text Display)                                                                         |

| 28   | 3.7.    | Text Display Mode with Increased Deflection Frequencies                                |

| 29   | 3.8.    | D2-MAC Operation Mode                                                                  |

| 29   | 3.8.1.  | Vertical Synchronization                                                               |

| 31   | 3.8.2.  | Calculation of S Correction and East–West Parabola and Pulsewidth Modulators           |

| 33   | 3.9.    | Subaddressing of the HSP Processor                                                     |

| 36   | 4.      | Application Notes                                                                      |

| 36   | 4.1.    | Clamping Circuit                                                                       |

| 36   | 4.2.    | Horizontal Sync Separation                                                             |

| 36   | 4.3.    | Vertical Sync Separation                                                               |

| 37   | 4.4.    | Synchronism Detector                                                                   |

| 37   | 4.5.    | PLL Filter Characteristics                                                             |

| 38   | 4.6.    | Blanking Pulses and Phase Adjustment                                                   |

| 39   | 4.6.1.  | 16:9 Picture Tube Format                                                               |

| 39   | 4.7.    | Control Loop II                                                                        |

| 40   | 4.8.    | Analog RGB Signals                                                                     |

| 40   | 4.9.    | Changing the Standard                                                                  |

| 41   | 5.      | Control and Status Registers                                                           |

| 47   | 5.1.    | Status and Control Registers of the HSP Processor                                      |

| 48   | 6.      | IM Bus                                                                                 |

#### **Deflection Processors**

Note: If not otherwise designated, the pin numbers mentioned refer to the 40-pin Dil package.

#### 1. Introduction

These programmable VLSI circuits in N-channel MOS technology carry out the deflection functions in digital color TV receivers based on the DIGIT 2000 system and are also suitable for text and D2-MAC application. The three types are basically identical, but are modified according to the intended application:

#### **DPU 2553**

normal-scan horizontal deflection, standard CTV receivers, also equipped with Teletext and D2-MAC facility

#### **DPU 2554**

double-scan horizontal deflection, for CTV receivers equipped with double-frequency horizontal deflection and double-frequency vertical deflection for improved picture quality. At power-up, this version starts with double horizontal frequency.

## 1.1. General Description

The DPU 2553/54 Deflection Processors contain the following circuit functions on one single silicon chip:

- video clamping

- horizontal and vertical sync separation

- horizontal synchronization

- normal horizontal deflection

- east-west correction, also for flat-screen picture tubes

- vertical synchronization

- normal vertical deflection

- sawtooth generation

- text display mode with increased deflection frequencies (18.7 kHz horizontal and 60 Hz vertical)

- D2-MAC operation mode

### and for DPU 2554 only:

- double-scan horizontal deflection

- normal and double—scan vertical deflection

In this data sheet, all information given for double—scan mode is available with the DPU 2554 only. Type DPU 2553 starts the horizontal deflection with 15.5 kHz according to the normal TV standard, whereas type DPU 2554 starts with 31 kHz according to the double—scan system.

The following characteristics are programmable:

- selection of the TV standard (PAL, D2-MAC or NTSC)

- selection of the deflection standard (Teletext, horizontal and vertical double—scan, and normal scan)

- filter time-constant for horizontal synchronization

- vertical amplitude, S correction, and vertical position for in-line, flat-screen and Trinitron picture tubes

- east—west parabola, horizontal width, and trapezoidal correction for in–line, flat—screen and Trinitron picture tubes

- switchover characteristics between the different synchronization modes

- characteristic of the synchronism detector for PLL switching and muting

## 1.2. Environment

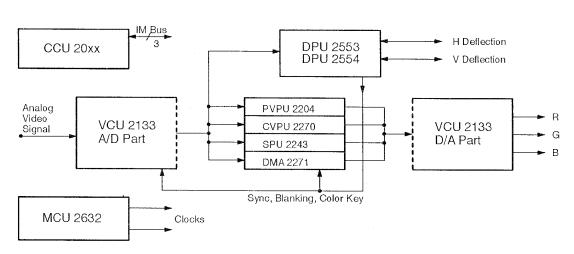

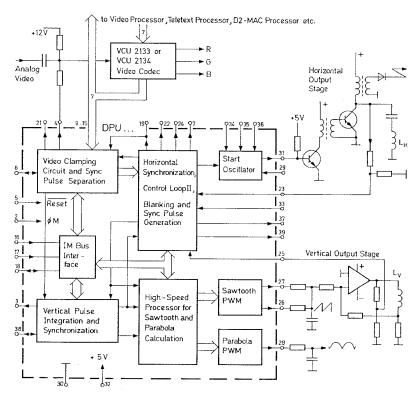

Fig. 1–1 shows the simplified block diagram of the video and deflection section of a digital TV receiver based on the DIGIT 2000 system. The analog video signal derived from the video detector is digitized in the VCU 2133, VCU 2134 or VCU 2136 Video Codec and supplied in a parallel 7 bit Gray code. This digital video signal is fed to the video section (PVPU, CVPU, SPU and DMA) and to the DPU 2553/54 Deflection Processor which carries out all functions required in conjunction with deflection, from sync separation to the control of the deflection power stages, as described in this data sheet.

Fig. 1–1: Block diagram of the video and deflection section of a digital TV receiver according to the DIGIT 2000 concept

# 2. Specifications

# 2.1. Outline Dimensions

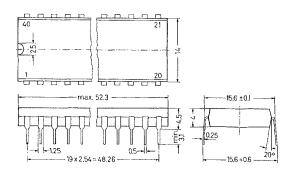

Fig. 2–1: DPU 2553 and DPU 2554 in 40-pin Dil plastic package, 20 B 40 according to DIN 41 870

Weight approx. 6 g,

Dimensions in mm

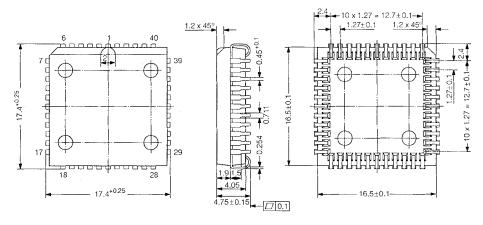

Fig. 2-2: DPU 2553 and DPU 2554 in 44-pin PLCC Package,

Weight approx. 2.2 g, Dimensions in mm

# 2.2. Pin Connections

|       |                                                                                        | 7  | 1H and 2H Skew Data Output |

|-------|----------------------------------------------------------------------------------------|----|----------------------------|

| 2.2.1 | . 40-Pin Dil Package                                                                   | 8  | Leave Vacant               |

| 1     | Leave Vacant                                                                           | 9  | V6 Video Input (MSB)       |

| 2     | ΦM Main Clock Input                                                                    | 10 | V5 Video Input             |

| 3     | Output for Single-Scan Vertical Blanking Pulse                                         | 11 | V4 Video Input             |

| 4     | Clamping Output 2                                                                      | 12 | V3 Video Input             |

| 5     | Reset Input                                                                            | 13 | V2 Video Input             |

| 6     | Input for the D2–MAC Composite Sync Signal and Output for the Separated Composite Sync | 14 | V1 Video Input             |

|       | Signal                                                                                 | 15 | V0 Video Input (LSB)       |

# DPU 2553, DPU 2554

| 16 | IM Bus Clock Input                                                                        | 3  | Vertical Blanking & Delayed Horizontal Blanking                                      |

|----|-------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------|

| 17 | IM Bus Ident Input                                                                        |    | Pulse Output                                                                         |

| 18 | IM Bus Data Input/Output                                                                  | 4  | Horizontal Flyback Input                                                             |

| 19 | Combined Output for the Color Key Pulse and the                                           | 5  | Undelayed Horizontal Blanking Pulse Output                                           |

| 00 | Undelayed Horizontal Blanking Pulse                                                       | 6  | Vertical Flyback Safety Input                                                        |

| 20 | HSP Status Output                                                                         | 7  | Vertical Flyback Output                                                              |

| 21 | Clamping Output 1                                                                         | 8  | Vertical Sawtooth Output                                                             |

| 22 | Combined Output for the Delayed Horizontal Blanking Pulse and the Vertical Blanking Pulse | 9  | East/West Parabola Output                                                            |

| 23 | Horizontal Flyback Input                                                                  | 10 | Horizontal Output Polarity & Pulsewidth Select Input                                 |

| 24 | Undelayed Horizontal Blanking Output                                                      | 11 | Ground                                                                               |

| 25 | Vertical Flyback Safety Input                                                             | 12 | Ground                                                                               |

| 26 | Vertical Flyback Output                                                                   | 13 | Horizontal Output                                                                    |

| 27 | Vertical Sawtooth Output                                                                  | 14 | V <sub>SUP</sub>                                                                     |

| 28 | East-West Parabola Output                                                                 | 15 | External Standard Selection Input                                                    |

| 29 | Horizontal Output Polarity Select Input and Start Oscillator Pulsewidth Select Input      | 16 | Start Oscillator Clock Input                                                         |

| 30 | Ground                                                                                    | 17 | V <sub>SUP</sub> (Start Oscillator)                                                  |

| 31 | Horizontal Output                                                                         | 18 | Start Oscillator Select Input                                                        |

| 32 | V <sub>SUP</sub> Supply Voltage                                                           | 19 | Horizontal Power Stage Control Switch Output                                         |

| 33 | External Standard Selection Input                                                         | 20 | Leave Vacant (Test Pin)                                                              |

| 34 | Start Oscillator Clock Input                                                              | 21 | Interlace Control Output                                                             |

| 35 | Start Oscillator Supply Voltage                                                           | 22 | Leave Vacant                                                                         |

| 36 | Start Oscillator Select Input                                                             | 23 | Leave Vacant                                                                         |

| 37 | Control Switch Output for the Horizontal Power Stage                                      | 24 | Leave Vacant                                                                         |

| 38 | Test Pin, leave vacant                                                                    | 25 | ФМ Main Clock Input                                                                  |

| 39 | Interlace Control Output                                                                  | 26 | Single-Scan Vertical Blanking Pulse Output                                           |

| 40 | Leave Vacant                                                                              | 27 | Clamping Output 2                                                                    |

| +0 | Leave vacant                                                                              | 28 | Reset Input                                                                          |

|    | 2. 44–Pin PLCC Package                                                                    | 29 | Input for the D2-MAC Composite Sync Signa and Output for the Separated Composite Syn |

| 1  | Leave Vacant                                                                              |    | Signal                                                                               |

| 2  | Clamping Output 1                                                                         | 30 | 1H and 2H Skew data Output                                                           |

|    |                                                                                           |    |                                                                                      |

- 31 Leave Vacant

- 32 V6 Video Input (MSB)

- 33 V5 Video Input

- 34 V4 Video Input

- 35 V3 Video Input

- 36 V2 Video Input

- 37 V1 Video Input

- 38 V0 Video Input (LSB)

- 39 IM Bus Clock Input

- 40 Substrate

- 41 IM Bus Ident input

- 42 IM Bus Data Input/Output

- 43 Undelayed Horizontal Blanking & Color Key Pulse Output

- 44 HSP Status Output

# 2.3. Pin Descriptions (pin numbers for 40-pin DIL package)

Pin 30 – Ground

This pin must be connected to the negative of the supply.

Pin 2 –  $\Phi$ M Main Clock Input (Fig. 2–5)

By means of this input, the DPU receives the required main clock signal from the MCU 2600 or MCU 2632 Clock Generator IC.

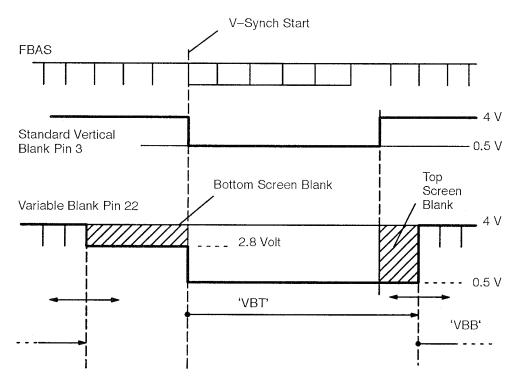

Pin 3 – Single–Scan Vertical Blanking Output (Fig. 2–12) In vertical double–scan mode, this pulse is also required by the CVPU 2270 Comb Filter Video Processor.

Pins 4 and 21 – Clamping Outputs 2 and 1 (Fig. 2–11) These pins supply pulses for clamping the video signal at the VCU 2133, VCU 2134 or VCU 2136 during the back porch.

Pin 5 - Reset Input (Fig. 2-3)

This pin is used for hardware reset. At low level, reset is actuated, and at high level the DPU is ready for communication with the CCU via the IM bus.

Pin 6 – Input for the D2–MAC composite Sync Signal and Output for the Separated Composite Sync Signal This pin (Fig. 2–10) is the input for the D2–MAC composite sync signal and the output for the separated composite sync signal.

Pin 7 – Skew Data Output (Fig. 2–12)

This pin delivers the 1H and 2H skew data stream required by the PSP 2210 Progressive Scan Processor and the TPU 2735 or TPU 2740 Teletext Processor or others for adjusting the phase of the double—scan video signal and for information about vertical sync.

Pin 32 - V<sub>SUP</sub> Supply Voltage

This pin must be connected to the positive of the supply.

Pins 9 to 15 - V6 to V0 Video Inputs (Fig. 2-4)

Via these pins, the DPU receives the digitized composite video signal from the VCU 2133, VCU 2134 or VCU 2136 Video Codec in a parallel 7–bit Gray code. With a standard signal, the sync pulse resolution is 6 bits.

Pins 16 to 18 – IM Bus Connections

These pins connect the DPU to the IM bus. It is via the IM bus that the DPU communicates with the CCU. Pins 16 (IM Bus Clock Input) and 17 (IM Bus Ident Input) have the configuration shown in Fig. 2–3. Pin 18 (IM Bus Data Input/Output) is shown in Fig. 2–10.

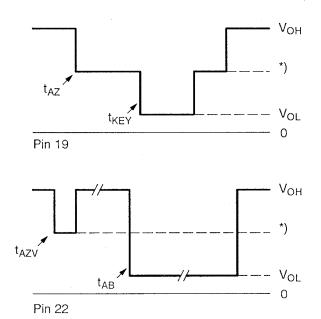

Pin 19 – Combined Output for the Color Key Pulse and the Undelayed Horizontal Blanking Pulse (Fig. 2–12) This output is tristate—controlled. In conjunction with the input load represented by the VCU, the three—level key and blanking pulse is produced which is also needed by the other DIGIT 2000 processors.

Pin 20 – HSP Status Output (Fig. 2–13)

This output supplies a HSP status signal. If this pin is low, a malfunction of the internal HSP-processor is indicated, which may be caused by power or clock problems. This output will stay low until two hardware or software resets of the DPU occur.

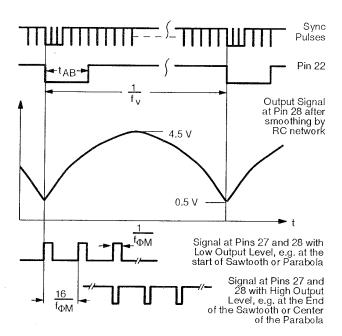

Pin 22 – Combined Output for the Delayed Horizontal Blanking Pulse and the Vertical Blanking Pulse (Fig. 2–12)

This pin is a tristate—controlled output. In conjunction with the input load represented by the VCU, the three–level combined blanking pulse is produced which is also needed by the other DIGIT 2000 processors.

Pin 23 – Horizontal Flyback Input (Fig. 2–6)

Pin 23 requires horizontal flyback pulses which must be clamped by a diode to the +5 V supply.

Pin 24 – Undelayed Horizontal Blanking Output (Fig. 2–12)

This output supplies undelayed horizontal blanking pulses. These pulses are for keying of the IF amplifier and are keying pulses for the VCU.

Pin 25 - Vertical Flyback Safety Input (Fig. 2-6)

To protect the picture tube from damage by burn—in in the event of a malfunction of the vertical deflection, an acknowledge pulse derived from the vertical deflection yoke is fed to pin 25. If this pulse exceeds the 2.5 V threshold during vertical blanking, the blanking pulse will be terminated. If it is planned to operate without this picture tube protection, pin 25 must be connected to +5 V.

## Pin 26 – Vertical Flyback Output (Fig. 2-14)

This pin supplies the same pulsewidth—modulated sawtooth signal as pin 27, but only for 350  $\mu$ s from the start of the vertical flyback. During the remaining time, pin 26 is used for fast charge—reversal of the integration capacitor.

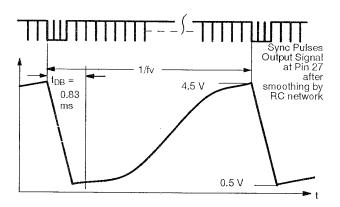

#### Pin 27 - Vertical Sawtooth Output (Fig. 2-14)

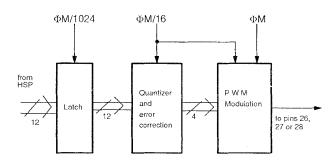

This pin supplies the signal, in pulsewidth—modulated form, for driving the vertical output stage. To produce the analog sawtooth signal, this signal must be integrated externally, e.g. by an RC network. By way of the IM bus interface and the HSP processor, it is possible for this sawtooth to be varied by the CCU.

# Pin 28 – East–West Parabola Output (Fig. 2–14)

This pin supplies the vertical–frequency parabola signal for the east–west correction in pulsewidth–modulated form. Via the IM bus and the HSP processor, the east–west parabola can be adjusted by the CCU.

# Pin 29 – Horizontal Output Polarity and Pulsewidth Select Input (Fig. 2–7)

This pin serves for selecting the polarity and the pulsewidth of the output pulses of pin 31 as described in section 3.4. This pin must be connected to ground or to +5 V.

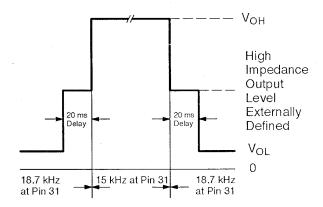

## Pin 31 – Horizontal Output (Fig. 2–11)

This output supplies the driving pulses for the horizontal output stage. The output pulse polarity can be selected by means of pin 29.

# Pin 33 – External Standard Selection Input (Fig. 2–8) This input is used for selecting the horizontal frequency standard, as shown in Table 3-3. If pin 33 is +5 V, the DPU operates only with the NTSC standard. If it is connected to ground, however, the DPU is set for the PAL or SECAM standard, and the horizontal standard can only be changed by the CCU command between PAL/ SECAM and text display mode. If pin 33 is unconnected, all standards can be selected by the CCU via the IM bus. Furthermore, when pin 33 is unconnected, the horizontal protection circuit6 is in effect, and for this a 4 MHz signal is required at pin 34. In this case, the output pulse at pin 31 is limited to a maximum duration of 30 µs for all standards. The phase resolution of the trailing edge of this pulse is reduced to 250 ns, if the output pulse is set to more than 30 µs pulsewidth.

# Pin 34 – Protection Circuit Clock Input (Fig. 2–9) When pin 33 is left unconnected, a 4 MHz clock signal is required at pin 34 for the horizontal protection circuit. The 4 MHz clock can be fed to pin 34 via a capacitor, and is available, e.g., at pin 1 of the CCU at no added cost. If the 4 MHz signal is not present and pin 33 is not connected, the horizontal output pin 31 is undefined.

## Pin 35 - Start Oscillator Supply

Via this pin it is possible with minimum current consumption to operate the horizontal protection circuit as a starting oscillator. For this purpose only the 4 MHz signal at pin 34 is required. Pin 36 must be connected to pin 35.

# Pin 36 - Start Oscillator Select Input (Fig. 2-7)

If the start oscillator function is required (see Table 3–3), pin 36 must be connected to pin 35. If the start oscillator function is not used, pin 36 has to be connected to ground. In this mode, the horizontal output pin 31 is switched off (at high level) as long as the Reset input pin 5 is Low.

# Pin 37 – Control Switch Output for the Horizontal Power Stage (Fig. 2–12)

This pin serves for switching over the horizontal output stage to another frequency.

#### Pin 38 – Test pin

This pin is an input/output of the type shown in Fig. 2–10. It i used for testing the DPU during production and should be left unconnected in normal operation.

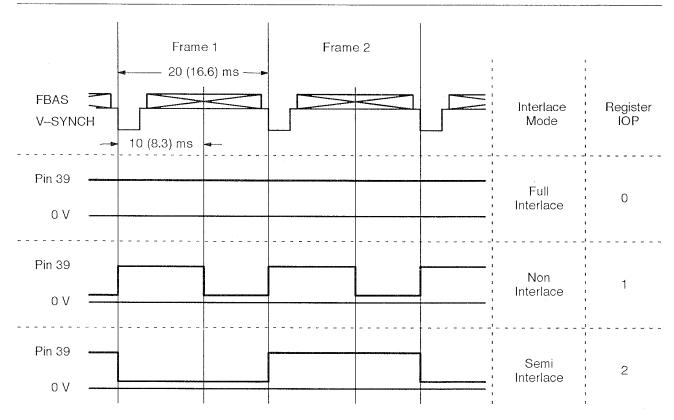

# Pin 39 – Interlace Control Output (Fig. 2–11)

This pin is for controlling an AC coupled vertical power stage for interlace—free mode (with DPU 2553) and for AC and DC coupled vertical power stage for the three interlace modes with the VMC—Processor

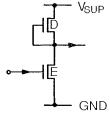

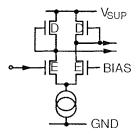

# 2.4. Pin Circuits (pin numbers for 40-pin DIL package)

The following figures schematically show the circuitry at the various pins. The integrated protection structures are not shown. The letter "E" means enhancement, the letter "D" depletion, and "S" stands for signal.

Fig. 2–3: Input Pins 5, 16 and 17

Fig. 2–4: Input Pins 9 to 15

# DPU 2553, DPU 2554

# 2.5. Electrical Characteristics (pin numbers for 40-pin DIL package)

All voltages are referred to ground.

# 2.5.1. Absolute Maximum Ratings

| Symbol           | Parameter                     | Pin No.                                               | Min.   | Max.                     | Unit |

|------------------|-------------------------------|-------------------------------------------------------|--------|--------------------------|------|

| T <sub>A</sub>   | Ambient Operating Temperature | _                                                     | 0      | 65                       | °C   |

| T <sub>S</sub>   | Storage Temperature           | _                                                     | -40    | +125                     | °C   |

| V <sub>SUP</sub> | Supply Voltage                | 32                                                    | _      | 6                        | V    |

| V <sub>I</sub>   | Input Voltage, all Inputs     | _                                                     | -0.3 V | V <sub>SUP</sub> + 0.3 V | _    |

| Vo               | Output Voltage                | 3, 6, 7,<br>18, 19,<br>22, 24,<br>26 to 28,<br>37, 38 | -0.3 V | V <sub>SUP</sub> + 0.3 V | _    |

| Vo               | Output Voltage                | 4, 21                                                 | -0.3   | +9                       | V    |

| Vo               | Output Voltage                | 31, 39                                                | -0.3   | +11                      | V    |

| lo               | Output Current                | 4, 18,<br>21, 39                                      | _      | 10                       | mA   |

| lo               | Output Current                | 20                                                    |        | 1                        | mA   |

| lo               | Output Current                | 31                                                    | _      | 50                       | mA   |

| lo               | Output Current                | 3, 6, 7,<br>19, 22,<br>24,<br>26 to 28,<br>37, 38     | _      | *)                       | _    |

<sup>\*)</sup> These outputs are short, circuit proof with respect to supply and ground

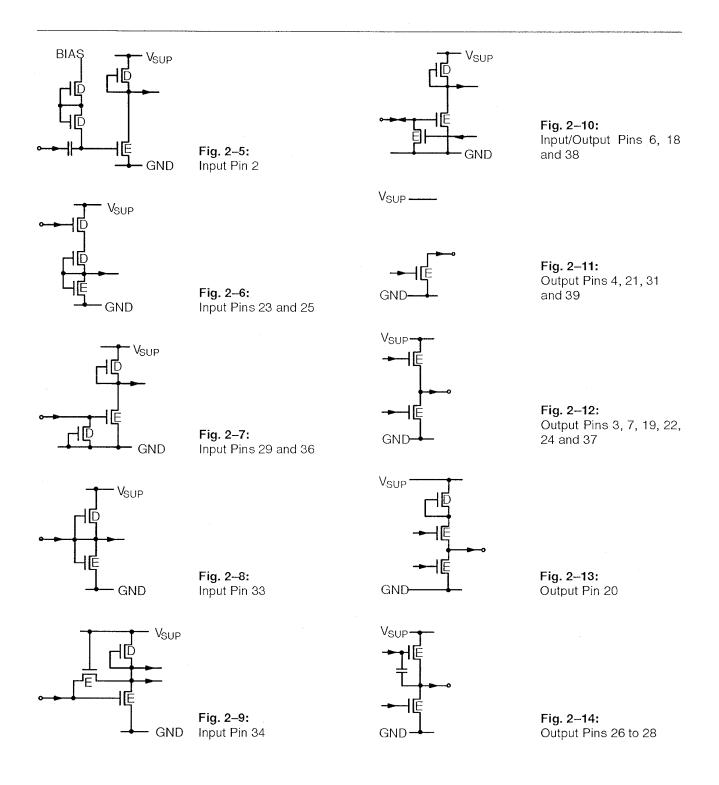

# **2.5.2. Recommended Operating Conditions** at $T_A = 0$ to 65 °C, $f_{\Phi M} = 14.3$ to 20.5 MHz

| Symbol                           | Parameter                                             | Pin No.    | Min.                                 | Тур. | Max.                                 | Unit |

|----------------------------------|-------------------------------------------------------|------------|--------------------------------------|------|--------------------------------------|------|

| V <sub>SUP</sub>                 | Supply Voltage                                        | 32         | 4.75                                 | 5.0  | 5.25                                 | V    |

| $V_{\Phi MIDC}$                  | ΦM Clock Input D.C. Voltage                           | 2          | 1.5                                  | _    | 3.5                                  | V    |

| $V_{\Phi MIAC}$                  | ФМ Clock Input<br>A.C. Voltage (p-p)                  |            | 0.8                                  | _    | 2.5                                  | V    |

| $rac{t_{\PhiMIH}}{t_{\PhiMIL}}$ | ΦM Clock Input<br>High/Low Ratio                      |            | 0.9                                  | 1.0  | 1.1                                  | _    |

| $t_{\PhiMIHL}$                   | ФМ Clock Input<br>High to Low Transition Time         |            | •                                    | -    | 0.15<br>f <sub>ΦD</sub>              | _    |

| $t_{\PhiMILH}$                   | ФМ Clock Input<br>Low to High Transition Time         |            | _                                    |      | 0.15<br>f <sub>ΦD</sub>              | _    |

| V <sub>VIL</sub>                 | Video Input Low Voltage                               | 9 to 15    | _                                    |      | 0.5 ·<br>V <sub>SUP</sub><br>+ 0.3 V | _    |

| V <sub>VIH</sub>                 | Video Input High Voltage                              |            | 0.5 ·<br>V <sub>SUP</sub><br>+ 0.3 V |      |                                      | _    |

| t <sub>ФVIH</sub>                | Video Input Setup Time<br>after ФМ Clock Input        | 9 to 15, 2 | 8                                    |      | _                                    | ns   |

| t <sub>VISΦ</sub>                | Video Input Setup Time<br>before ΦM Clock Input       |            | 8                                    |      | _                                    | ns   |

| V <sub>REIL</sub>                | Reset Input Low Voltage                               | 5          | _                                    | _    | 1.2                                  | V    |

| V <sub>REIH</sub>                | Reset Input High Voltage                              |            | 2.4                                  |      | _                                    | V    |

| V <sub>D2IL</sub>                | D2-MAC Sync Input Low Voltage                         | 6          | _                                    | _    | 0.8                                  | V    |

| V <sub>D2IH</sub>                | D2-MAC Sync Input High Voltage                        |            | 2.4                                  |      | _                                    | V    |

| V <sub>IMIL</sub>                | IM Bus Input Low Voltage                              | 16 to 18   | _                                    | _    | 0.8                                  | V    |

| V <sub>IMIH</sub>                | IM Bus Input High Voltage                             |            | 2.4                                  | _    | _                                    | V    |

| $f_{\PhiI}$                      | ФI IM Bus Clock Frequency                             |            | 0.05                                 | _    | 170                                  | kHz  |

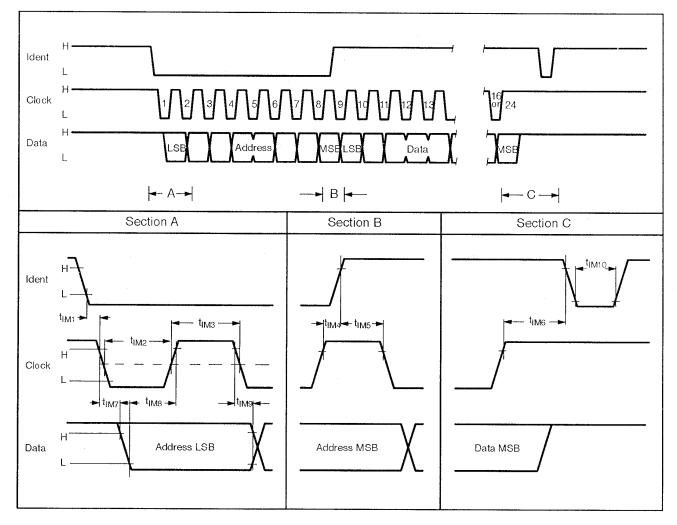

| t <sub>IM1</sub>                 | ΦI Clock Input Delay Time<br>after IM Bus Ident Input |            | 0                                    | _    |                                      | _    |

| t <sub>IM2</sub>                 | ΦI Clock Input Low Pulse Time                         |            | 3.0                                  | _    | _                                    | μs   |

| t <sub>IM3</sub>                 | ФI Clock Input High Pulse Time                        |            | 3.0                                  | _    | _                                    | μs   |

| t <sub>IM4</sub>                 | ◆I Clock Input Setup Time before Ident Input High     |            | 0                                    | _    |                                      | _    |

| t <sub>IM5</sub>                 | ФI Clock Input Hold Time<br>after Ident Input High    |            | 1.5                                  | _    | -                                    | μs   |

# Recommended Operating Conditions, continued

| Symbol              | Parameter                                                | Pin No.  | Min.  | Тур. | Max. | Unit |

|---------------------|----------------------------------------------------------|----------|-------|------|------|------|

| t <sub>IM6</sub>    | ФI Clock Input Hold Time<br>before Ident End-Pulse Input | 16 to 18 | 6.0   | _    | _    | μs   |

| t <sub>IM7</sub>    | IM Bus Data Input Delay Time<br>after ФI Clock Input     |          | 0     | _    | _    |      |

| t <sub>IM8</sub>    | IM Bus Data Input Setup Time<br>before ΦI Clock Input    |          | 0     |      |      | _    |

| t <sub>IM9</sub>    | IM Bus Data Input Hold Time<br>after ⊕I Clock Input      |          | 0     |      | _    | _    |

| <sup>t</sup> lM10   | IM Bus Ident End-Pulse Low Time                          |          | 3.0   | _    | _    | μs   |

| V <sub>HFIL</sub> . | Horizontal Flyback Input<br>Low Voltage                  | 23       |       | _    | 0.8  | V    |

| V <sub>HFIH</sub>   | Horizontal Flyback Input<br>High Voltage                 |          | 3.2*) | _    | _    | V    |

| V <sub>VFSIL</sub>  | Vertical Flyback Safety Input<br>Low Voltage             | 25       | _     | _    | 1.5  | V    |

| V <sub>VFSIH</sub>  | Vertical Flyback Safety Input<br>High Voltage            |          | 3.5   | _    | _    | V    |

| V <sub>SIL</sub>    | Select Input Low Voltage                                 | 29, 33,  | _     | _    | 0.8  | V    |

| . V <sub>SIH</sub>  | Select Input High Voltage                                | 36       | 2.4   |      | _    | V    |

| V <sub>soci</sub>   | Start Oscillator Clock Input Voltage (p-p), A.C. Coupled | 34       | 0.5   | _    | _    | V    |

| f <sub>soc</sub>    | Start Oscillator Clock Frequency                         |          | _     | _    | _    | MHz  |

<sup>\*)</sup> Pin 23 must be clamped to the +5 V supply by means of a diode (anode of the diode to pin 23).

# **2.5.3. Characteristics** at T<sub>A</sub> = 0 to 65 °C, V<sub>SUP</sub> = 4.75 to 5.25 V, $f_{\Phi M}$ = 14.3 to 20.5 MHz

| Symbol           | Parameter                                                                                               | Pin No.        | Min.         | Тур.           | Max.         | Unit                                  | Test Conditions                           |

|------------------|---------------------------------------------------------------------------------------------------------|----------------|--------------|----------------|--------------|---------------------------------------|-------------------------------------------|

| ISUP             | Supply Current                                                                                          | 32             | -            | 160            | 205          | mA                                    |                                           |

| I <sub>SUP</sub> | Supply Current                                                                                          | 35             | _ `          | 2.5            | 5            | mA                                    |                                           |

| VIMOL            | IM Bus Output Low Voltage                                                                               | 18             | _            | -              | 0.4          | V                                     | I <sub>IMO</sub> = 3 mA                   |

| IIMOH            | IM Bus Output High Current                                                                              |                |              | _              | 10           | μА                                    | V <sub>IMO</sub> = 5 V                    |

| Values refe      | Circuit and Pulse Separation<br>rred to an analog composite video sigr<br>36 Video Codec (see Fig. 3–2) | nal of 2 V (p- | -p), whose p | ootential is b | etween 5 ar  | nd 7 V at pir                         | 37 of the VCU 2133, VCU 21                |

|                  |                                                                                                         |                |              |                | <del>,</del> | · · · · · · · · · · · · · · · · · · · |                                           |

| V <sub>CL</sub>  | Clamping Level of the Sync<br>Pulse Top                                                                 | -              |              | 5.125          | _            | V                                     | non–synchronized<br>horizontal deflection |

| Symbol              | Parameter                                                                                | Pin No.          | Min.     | Тур.         | Max.       | Unit   | Test Conditions                                                    |

|---------------------|------------------------------------------------------------------------------------------|------------------|----------|--------------|------------|--------|--------------------------------------------------------------------|

| V <sub>SPSNS</sub>  | Sync Pulse Separation Level                                                              | _                | _        | 5.25         | _          | V      | non–synchronized<br>horizontal deflection                          |

| V <sub>SPSS</sub>   | Sync Pulse Separation Level                                                              | _                | 50 % of  | the sync pul | se amplit. | -      | synchronized<br>horizontal deflection                              |

| t <sub>CPD</sub>    | Clamping Pulse Duration                                                                  | 4, 21            | _        | 0.86         | -          | μs     |                                                                    |

| R <sub>CLON</sub>   | Clamping Pulse Output<br>ON Resistance                                                   |                  | _        | -            | 150        | Ω      | I <sub>CLO</sub> = 5 mA                                            |

| ICLOFF              | Clamping Pulse Output<br>OFF Current                                                     |                  | _        |              | 10         | Аij    | V <sub>CLO</sub> = 8 V                                             |

| <sup>‡</sup> СРРН   | Clamping Pulse Phase Position                                                            | 4, 21<br>9 to 15 | _        | 6.49         | _          | μs     | referred to the center of the sync pulse in the input video signal |

| f <sub>cor</sub>    | Corner Frequency of the Digital<br>Lowpass Filter Following the<br>Video Inputs V0 to V6 | 9 to 15          | _        | 1            | -          | MHz    |                                                                    |

| Horizontal          | Synchronization                                                                          |                  |          |              |            |        |                                                                    |

| t <sub>HO</sub>     | Horizontal Output Pulse<br>Duration                                                      | 31               | 1        | -            | 63         | μs     | variable in steps of 1 μs                                          |

| R <sub>HOON</sub>   | Horizontal Output<br>ON Resistance                                                       |                  | _        | _            | 40         | Ω      | I <sub>HO</sub> = 10 mA                                            |

| l <sub>HOOF</sub>   | Horizontal Output OFF Current                                                            |                  | _        | ***          | 10         | μА     | V <sub>HO</sub> = 10 V                                             |

| V <sub>CSOL</sub>   | Control Switch Output<br>Low Voltage                                                     | 37               | _        | _            | 0.4        | V      | I <sub>CSO</sub> = 5 mA                                            |

| Vcsoн               | Control Switch Output<br>High Voltage                                                    |                  | 4.0      | -            | -          | V      | -I <sub>CSO</sub> = 1.5 mA                                         |

| V <sub>сѕоні</sub>  | Control Switch Output High<br>Impedance Current                                          |                  | -10      | _            | +10        | μА     | V <sub>O</sub> = 0 to +5 V                                         |

| for                 | Capture Range and Frequency<br>Borders of the Horizontal PLL                             | _                | 15625 H  | z ± 800 Hz   |            | _      | DPU 2553<br>for PAL, SECAM and<br>D2-MAC                           |

|                     |                                                                                          |                  | 31250 H  | z ± 1600 Hz  |            | -      | DPU 2554<br>for PAL, SECAM and<br>D2-MAC                           |

|                     |                                                                                          |                  | 15734 H  | z ± 750 Hz   |            | _      | DPU 2553 for NTSC                                                  |

|                     |                                                                                          |                  | 31 468 F | lz ± 1500 H: | Z          | AMAN . | DPU 2554 for NTSC                                                  |

|                     |                                                                                          |                  | 18746, 8 | 02 Hz ± 400  | ) Hz       | _      | for Text Display Mode                                              |

| DR <sub>CL/HO</sub> | Divider Ratio between<br>ΦM Clock Frequency and                                          | 2, 31            | -        | 946          | _          | _      | for Text Display Mode<br>with f <sub>ΦM</sub> = 17.734475 MHz      |

|                     | 1 Horizontal Output Frequency<br>fHO                                                     |                  | _        | 1296         |            | -      | for D2–MAC Mode<br>with f <sub>ΦM</sub> = 20.25 MHz                |

|                     |                                                                                          |                  | -        | 1135.0064    |            | -      | for PAL and SECAM with f <sub>ФM</sub> = 17.734475 MHz             |

|                     |                                                                                          |                  | _        | 910          | _          | _      | for NTSC<br>with f <sub>ΦM</sub> = 14.31818 MHz                    |

# DPU 2553, DPU 2554

| Symbol             | Parameter                                                                                                       | Pin No.        | Min.          | Тур.          | Max.        | Unit                         | Test Conditions                                                 |

|--------------------|-----------------------------------------------------------------------------------------------------------------|----------------|---------------|---------------|-------------|------------------------------|-----------------------------------------------------------------|

| D <sub>SON</sub>   | Switch-On Delay for Horizontal<br>Color-Locking                                                                 | _              | _             | 10            | _           | s                            | for PAL and SECAM                                               |

|                    |                                                                                                                 |                | -             | 8.5           | _           | s                            | for NTSC                                                        |

| D <sub>SOF</sub>   | Switch-Off Delay for Horizontal<br>Color-Locking                                                                | -              |               | 80            | _           | ms                           | for PAL and SECAM                                               |

|                    |                                                                                                                 | :              |               | 66            | _           | ms                           | for NTSC                                                        |

| D <sub>HO/FL</sub> | Admissible Delay between<br>Hor. Output Pulse (Pin 31) and                                                      | 31, 23         | 0             | _             | 15          | fre                          | DPU 2553                                                        |

|                    | Hor. Flyback Pulse (Pin 23)                                                                                     | ;              | 0             | -             | 10          | με                           | DPU 2554                                                        |

| Leading Edge       | on Between Center of the Horizontal<br>e of the Horizontal Flyback Pulse at<br>e PVPU/CVPU,PSP and/or DTI for 6 | Pin 23 assur   | ming that the | e Digital Cou | mposite Vid | o 15 and the<br>eo Signal is |                                                                 |

| tsz                | Phase Position                                                                                                  | 9 to 15,<br>23 | _             | -0.22         | _           | με                           | DPU 2553 for PAL and<br>SECAM, t <sub>HFL</sub> = 12 μs         |

| t <sub>SZ</sub>    | Phase Position                                                                                                  |                | _             | -0.22         | -           | με                           | <b>DPU 2554</b> for PAL and<br>SECAM, t <sub>HFL</sub> = 6.2 μs |

| tsz                | Phase Position                                                                                                  |                |               | -0.98         | ~           | μs                           | <b>DPU 2553</b> for NTSC,<br>t <sub>HFL</sub> = 11 μs           |

| t <sub>SZ</sub>    | Phase Position                                                                                                  |                | _             | -0.54         | -           | μs                           | <b>DPU 2554</b> for NTSC,<br>t <sub>HFL</sub> = 5.75 μs         |

| Δt <sub>SZ</sub>   | Phase Setting Range                                                                                             |                | _             | ±3.5          | _           | μs                           | <b>DPU 2553</b><br>for PAL and SECAM                            |

| Δt <sub>SZ</sub>   | Phase Setting Range                                                                                             |                |               | ±1.75         | -           | μs                           | <b>DPU 2554</b><br>for PAL and SECAM                            |

| Δt <sub>SZ</sub>   | Phase Setting Range                                                                                             |                | _             | ±4.5          | _           | μs                           | DPU 2553 for NTSC                                               |

| Δt <sub>SZ</sub>   | Phase Setting Range                                                                                             |                | -             | ±2.25         | _           | μs                           | DPU 2554 for NTSC                                               |

| dt <sub>SZ</sub>   | Phase Setting Step Width                                                                                        | 9 to 15,<br>23 | _             | 0.225         | _           | με                           | <b>DPU 2553</b><br>for PAL and SECAM                            |

| dt <sub>SZ</sub>   | Phase Setting Step Width                                                                                        |                | _             | 0.11          | _           | με                           | DPU 2554<br>for PAL and SECAM                                   |

| dt <sub>SZ</sub>   | Phase Setting Step Width                                                                                        |                | _             | 0.28          | _           | με                           | DPU 2553 for NTSC                                               |

| dt <sub>SZ</sub>   | Phase Setting Step Width                                                                                        |                | _             | 0.14          | _           | μs                           | DPU 2554 for NTSC                                               |

| V <sub>SKOL</sub>  | Skew Data Output Low Voltage                                                                                    | 7              |               |               | 0.4         | V                            | I <sub>SKO</sub> = 12 mA                                        |

| V <sub>SKOH</sub>  | Skew Data Output High Voltage                                                                                   |                | 3.5           | _             | -           | V                            | -I <sub>SKO</sub> = 0.1 mA                                      |

| Symbol             | Parameter                                                                              | Pin No.  | Min.           | Тур.          | Max. | Unit | Test Conditions                    |

|--------------------|----------------------------------------------------------------------------------------|----------|----------------|---------------|------|------|------------------------------------|

| Vertical Syr       | nchronization                                                                          |          |                |               |      |      |                                    |

| R <sub>HSON</sub>  | HSP Status Output<br>ON Resistance                                                     | 20       | _              | _             | 10   | κΩ   | I <sub>HSO</sub> = 0.1 mA          |

| <sup>l</sup> HSOOF | HSP Status Output<br>OFF Resistance                                                    | 20       | _              | _             | 10   | μА   | V <sub>HSO</sub> = 5 V             |

| R <sub>ON</sub>    | Output ON Resistance                                                                   | 26 to 28 | -              | 100           |      | Ω    | $\pm l_O = 0.5 \text{ mA}$         |

| V <sub>ICL</sub>   | Interlace Control Output<br>Low Voltage                                                | 39       | _              | -             | 0.4  | V    | I <sub>IC</sub> = 6 mA             |

| lісн               | Interlace Control Output<br>High Current                                               |          |                |               | 10   | μА   | V <sub>IC</sub> = 5 V              |

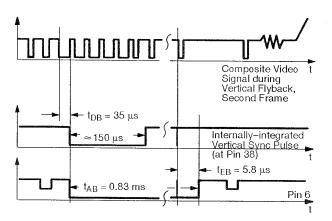

| t <sub>dB</sub>    | Delay of the Vertical Blanking<br>Pulse                                                | 22       | _              | 35            | _    | μs   | for PAL and SECAM, not locked      |

|                    |                                                                                        |          | _              | 4.5           | -    | hs   | for PAL and SECAM, locked          |

|                    |                                                                                        |          | _              | 35            |      | µs   | for NTSC, not locked               |

|                    |                                                                                        |          | -              | 36.5          | -    | μS   | for NTSC, locked                   |

| CRVS               | Capture Range of the Vertical<br>Synchronization Output                                | _        |                | 50 Hz ± 5 Hz  | Z    | _    | DPU 2553 for PAL, SECAM and D2-MAC |

|                    |                                                                                        |          |                | 100 Hz ± 10 F | -lz  |      | DPU 2554 for PAL, SECAM and D2-MAC |

|                    |                                                                                        |          |                | 60 Hz ± 6 H:  | Z    | -    | DPU 2553 for NTSC                  |

|                    |                                                                                        |          | 120 Hz ± 12 Hz |               |      | -    | DPU 2554 for NTSC                  |

| DR <sub>2H/V</sub> | Divider Ratio between Double                                                           | _        | _              | 625           | _    | -    | for PAL and SECAM                  |

|                    | the Horizontal Frequency and<br>the Vertical Frequency in the<br>Locked Operation Mode |          | _              | 525           | -    | -    | for NTSC                           |

|                    | Switch–On–Delay for the<br>Vertical Locking (adjustable)                               |          | _              | 624           | _    | _    | for Text Display Mode<br>(ZN = 0)  |

| D <sub>SON</sub>   | Switch-On-Delay for the                                                                |          | 1.3            |               | 2.5  | s    | for PAL and SECAM                  |

|                    | Vertical Locking (adjustable)                                                          |          | 1.7            | -             | 3.3  | s    | for NTSC                           |

| D <sub>SOF</sub>   | Switch-Off-Delay for the                                                               |          |                | 30/160/240/3  | 20   | ms   | for PAL and SECAM                  |

|                    | Vertical Locking (adjustable)                                                          |          | (              | 57/134/200/2  | 70   | ms   | for NTSC                           |

# DPU 2553, DPU 2554

| Symbol                      | Parameter                                                                   | Pin No. | Min.                | Тур.                        | Max.         | Unit     | Test Conditions               |

|-----------------------------|-----------------------------------------------------------------------------|---------|---------------------|-----------------------------|--------------|----------|-------------------------------|

| Key and Bla                 | anking Pulses                                                               |         |                     |                             |              |          |                               |

| V <sub>BOL</sub>            | 1 V Vertical Blanking Output<br>Low Voltage                                 | 3       | -                   | -                           | 0.4          | V        | I <sub>VBO</sub> = 1.6 mA     |

| V <sub>ВОН</sub>            | 1 V Vertical Blanking Output<br>High Voltage                                |         | 3.5                 | -                           | _            | V        | -I <sub>VBO</sub> = 0.1 mA    |

|                             | 1 V Vertical Blanking Output<br>Timing                                      |         |                     | iming as Pin<br>Scan Pulses |              | but      |                               |

| Undelayed I<br>Pulse Outpu  | Horizontal Blanking and Color Key<br>it                                     | 19      |                     |                             |              |          |                               |

| luhbol                      | Undelayed Horizontal Blanking<br>Pulse Output Low Level<br>(High Impedance) |         | -10                 | -                           | +10          | μΑ       | V <sub>UHBO</sub> = 0 to +5 V |

| V <sub>UНВОН</sub>          | Undelayed Horizontal Blanking<br>Pulse Output High Voltage                  |         | 4.0                 | _                           | _            | V        | -l <sub>UHBO</sub> = 0.1 mA   |

| t <sub>AZ1</sub>            | Undelayed Horizontal Blanking<br>Pulse Phase Position                       |         | _                   | 3.85                        | -            | μs       |                               |

| VckoL                       | Color Key Pulse Output<br>Low Voltage                                       |         | _                   | -                           | 0.4          | V        | I <sub>CKO</sub> = 6 mA       |

| V <sub>СКОН</sub>           | Color Key Pulse Output<br>High Voltage                                      |         | 4.0                 | _                           | _            | V        | -I <sub>CKO</sub> = 0.1 mA    |

| t <sub>VB1</sub>            | Color Key Pulse Phase Position                                              |         | _                   | 2.82                        | _            | μs       |                               |

| Delayed Hor<br>ing Pulse Ou | rizontal Blanking and Vertical Blank-<br>utput                              | 22      |                     |                             |              |          |                               |

| I <sub>DHBOL</sub>          | Delayed Horizontal Blanking<br>Pulse Output Low Level (High<br>Impedance)   |         | -10                 | -                           | +10          | μА       | V <sub>DHBO</sub> = 0 to +5 V |

| V <sub>DHBOH</sub>          | Delayed Horizontal Blanking<br>Pulse Output High Voltage                    |         | 4.0                 | -                           | -            | V        | -I <sub>DHBO</sub> = 0.1 mA   |

| t <sub>AZ2</sub>            | Delayed Horizontal Blanking<br>Pulse Phase Position                         |         | _                   | -1.26                       | _            | fra      | with BP = 19                  |

| V <sub>VBOL</sub>           | Vertical Blanking Pulse Output<br>Low Voltage                               |         |                     | _                           | 0.4          | V        | I <sub>VBO</sub> = 6 mA       |

| V <sub>VBOH</sub>           | Vertical Blanking Pulse Output<br>High Voltage                              |         | 4.0                 | _                           | _            | V        | -I <sub>VBO</sub> = 0.1 mA    |

|                             | Vertical Blanking Pulse Phase<br>Position                                   | 22      | see t <sub>DB</sub> | at Vertical S               | ynchronizati | on       |                               |

| $t_{AB}$                    | Vertical Blanking Pulse Duration                                            |         | -                   | 0.83                        | -            | ms       | for PAL and SECAM with        |

|                             |                                                                             |         | that is 18.5 lines  |                             |              |          | VBL=4                         |

|                             |                                                                             |         | _                   | 0.83                        | -            | ms       | for NTSC with VBL = 0         |

| V <sub>UHBOL</sub>          | Undelayed Horizontal Blanking<br>Pulse Output Low Voltage                   | 24      | _                   | that is 13 lin              | 0.4          | V        | I <sub>UHBO</sub> = 1.6 mA    |

| V <sub>UHBOH</sub>          | Undelayed Horizontal Blanking<br>Pulse Output High Voltage                  |         | 35                  | _                           | _            | V        | -I <sub>HBO</sub> = 0.1 mA    |

| 1.2                         | Undel. Hor. Blank. Pulse Timing                                             |         | Same Ti             | iming as Pin                | 19           | <u> </u> |                               |

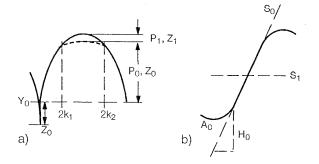

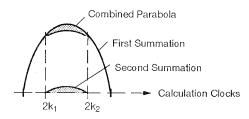

Table 2-1: Adjustment range and step width for the various adjustments for vertical single-scan mode

| Adjustable Quantity                   | Step Width | Adjustment Range     |

|---------------------------------------|------------|----------------------|

| Vertical Amplitude*)                  | 1 %        | ±20 %                |

| Vertical Linearity (S Curve)          | 0.1 %      | 0 to 20 %            |

| Point of Inflection of the S curve**) | 0.5 %      | 100 %                |

| Vertical Position                     | 0.1 %      | ±10 %                |

| Horizontal Amplitude                  | 0.4 %      | ±30 %                |

| Cushion Correction                    | 0.3 %      | Curvature 10 to 90 % |

| Trapezoidal Correction                | 0.1 %      | ±10 %                |

<sup>\*) 1 % = 2</sup> mm with a 26-inch picture tube

Fig. 2-15: Digital video input signals (pins 9 to 15)

<sup>\*\*)</sup> at 10 % linearity correction

# 3. Functional Description

## 3.1. Block Diagram

The DPU 2553 and DPU 2554 Deflection Processors perform all tasks associated with deflection in TV sets:

- sync separation

- generation and synchronization of the horizontal and the vertical deflection frequencies

- the various east-west corrections

- vertical sawtooth generation including S correction

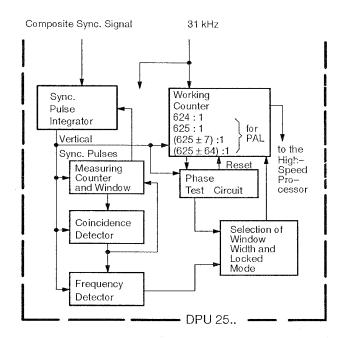

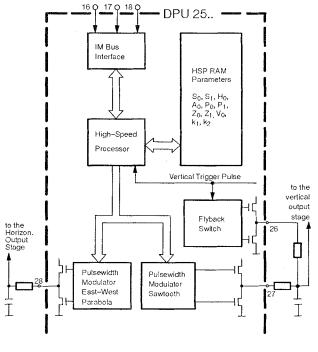

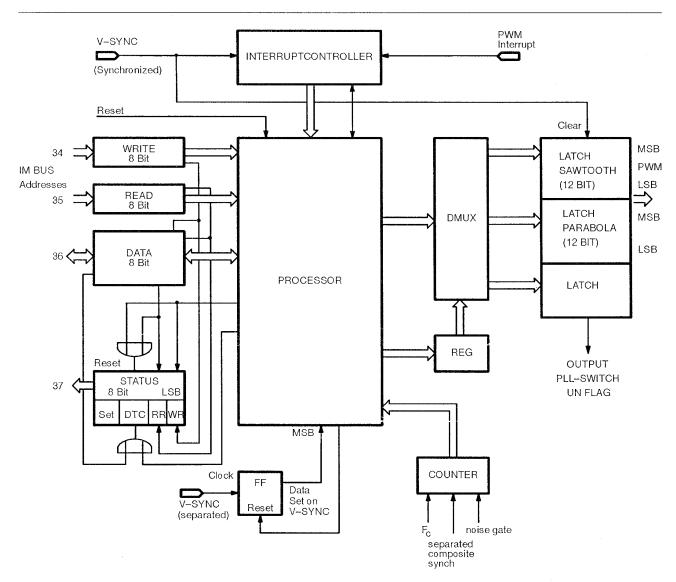

as described hereafter. The DPU communicates, via the bidirectional serial IM bus, with the CCU 2050 or CCU 2070 Central Control Unit and, via this bus, is supplied with the picture—correction alignment information stored in the MDA 2062 EEPROM during set production, when the set is turned on. The DPU is normally clocked with a trapezoidal 17.734 MHz (PAL or SECAM), or 14.3 MHz (NTSC) or 20.25 MHz (D2–MAC) clock signal supplied by the MCU 2600 or MCU 2632 Clock Generator IC. The functional diagram of the DPU is shown in Fig. 3–1.

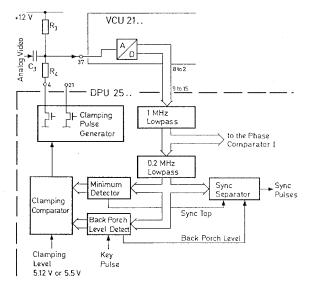

# 3.2. The Video Clamping Circuit and the Sync Pulse Separation Circuit

The digitized composite video signal delivered as a 7-bit parallel signal by the VCU 2133, VCU 2134 or VCU 2136 Video Codec is first noise-filtered by a 1 MHz digital low-

pass filter and, to improve the noise immunity of the clamping circuit, is additionally filtered by a 0.2 MHz low-pass filter before being routed to the minimum and back porch level detectors (Fig. 3–3).

The DPU has two different clamping outputs, No. 1 and No. 2, one of which supplies the required clamping pulses to the video input of the VCU as shown in Fig. 3–1. The following values for the clamping circuit apply for Video Amp. I. since the gain of Video Amp. II is twice that of Video Amp I, all clamping and signal levels of Video Amp II are half those of Video Amp I referred to +5 V.

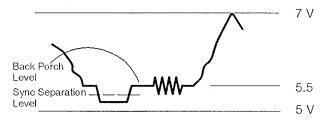

After the TV set is switched on, the video clamping circuit first of all ensures by means of horizontal—frequency current pulses from the clamping output of the DPU to the coupling capacitor of the analog composite video signal, that the video signal at the VCU's input is optimally biased for the operation range of the A/D converter of 5 to 7 V. For this, the sync top level is digitally measured and set to a constant level of 5.125 V by these current pulses. The horizontal and vertical sync pulses are now separated by a fixed separation level of 5.250 V so that the horizontal synchronization can lock to the correct phase (see section 3.3. and Figs. 3–2 and 3–3).

With the color key pulse which is now present in synchronism with the composite video signal, the video clamping circuit measures the DC voltage level of the porch and by means of the pulses from pin 21 (or pin4), sets the DC level of the porch at a constant 5.5 V (5.25 V for Video Amp II). This level is also the reference black

Fig. 3-1: Block diagram of the DPU 2553/54 Deflection Processors

level for the PVPU 2204 or CVPU 2270 Video Processors

When horizontal synchronization is achieved, the slice level for the sync pulses is set to 50 % of the sync pulse amplitude by averaging sync top and black level. This ensures optimum pulse separation, even with small sync pulse amplitudes (see application notes, section 4.).

Fig. 3-2: Levels in the video clamping circuit

Fig. 3–3: Principle of video clamping and pulse separation

#### 3.3. Horizontal Synchronization

Two operating modes are provided for in horizontal synchronization. The choice of mode depends on whether or not the TV station is transmitting a standard PAL or NTSC signal, in which there is a fixed ratio between color subcarrier frequency and horizontal frequency. In the first case we speak of "color–locked" operation and in the second case of "non–color–locked" operation (e.g. black–and–white programs). Switching between the two modes is performed automatically by the standard signal detector.

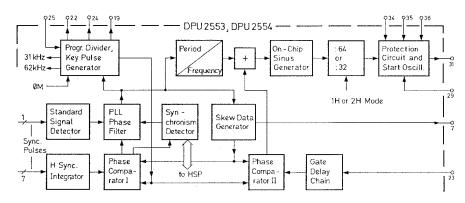

## 3.3.1. Non-Color-Locked Operation

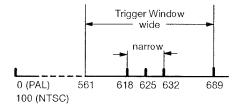

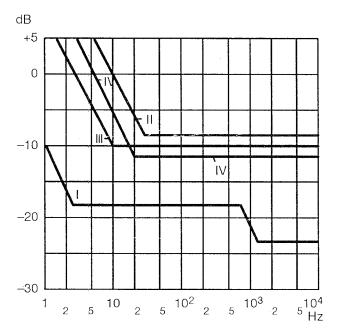

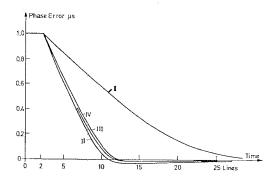

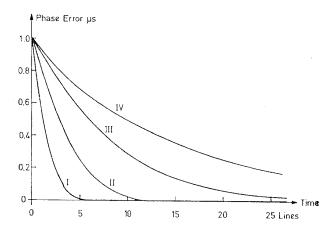

In the non-locked mode, which is needed in the situation where there is no standard fixed ratio between the color subcarrier frequency and the horizontal frequency of the transmitter, the horizontal frequency is produced by subdividing the clock frequency (17.7 MHz for PAL and SE-CAM, 14.3 MHz for NTSC) in the programmable frequency divider (Fig. 3-4) until the correct horizontal frequency is obtained. The correct adjustment of frequency and phase is ensured by phase comparator I. This determines the frequency and phase deviation by means of a digital phase comparison between the separated horizontal sync pulses and the output signal of the programmable divider and corrects the divider accordingly. For optimum adjustment of phase jitter, capture behavior and transient response of the horizontal PLL circuit, the measured phase deviation is filtered in a digital lowpass filter (PLL phase filter). In the case of nonsynchronized horizontal PLL, this filter is set to wideband PLL response with a pull-in range of ±800 Hz. If the PLL circuit is locked, the PLL filter is automatically switched to narrow-band response by an internal synchronism detector in order to limit the phase jitter to a minimum, even in the case of weak and noisy signals.

A calculator circuit in phase comparator I, which analyzes the edges of the horizontal sync pulses, increases the resolution of the phase measurement from 56 ns at 17.7 MHz clock frequency to approx. 6 ns, or from 70 ns at 14.3 MHz clock frequency to approx. 2.2 ns.

Fig. 3-4: Principle of the horizontal synchronization

The various key and gating pulses such as the color key pulse  $(t_{Key}), \ the \ normal-scan \ (1H) \ and \ double-scan \ (2H) \ horizontal blanking pulse <math display="inline">(t_{AZV})$  and the 1 H horizontal undelayed gating pulse  $(t_{AZV})$  are derived from the output signals of the programmable divider and an additional counter for the 2H signals and the 1H and 2H skew data output. These pulses retain a fixed phase position with respect to the 1H input video signal and the double-scan output video signal from the CVPU 2270 Video Processor.

For the purpose of equalizing phase changes in the horizontal output stage due to switching response tolerances or video influence, a second phase control loop is used which generates the horizontal output pulse at pin 31 to drive the horizontal output stage. In phase comparator II (Fig. 3-4), the phase difference between the output signal of the programmable divider and the leading edge (or the center) of the horizontal flyback pulse (pin 23) is measured by means of a balanced gate delay line. The deviation from the desired phase difference is used as an input to an adder. In this, the information on the horizontal frequency derived from phase comparator I is added to the phase deviation originating form phase comparator II. The result of this addition controls a digital on-chip sinewave generator (about 1 MHz) which acts as a phase shifter with a phase resolution of 1/128 of one main clock period  $\Phi M$ .

By means of control loop II the horizontal output pulse (pin 31) is shifted such that the horizontal flyback pulse (pin 23) acquires the desired phase position with respect to the output signal of the programmable divider which, in turn, due to phase comparator I, retains a fixed phase position with respect to the video signal. The horizontal output pulse itself is generated by dividing the frequency of the 1 MHz sinewave oscillator by a fixed ratio of 64 in the case of normal scan and of 32 in the case of double—scan operation.

## 3.3.2. Color-Locked Operation

When in the color-locked operating mode, after the phase position has been set in the non-color-locked mode, the programmable divider is set to the standard division ratio (1135:1 for PAL, 910:1 for NTSC) and phase comparator I is disconnected so that interfering pulses and noise cannot influence the horizontal deflection. Because phase comparator II is still connected, phase errors of the horizontal output stage are also corrected in the color-locked operating mode. The standard signal detector is so designed that it only switches to color-locked operation when the ratio between color subcarrier frequency and horizontal frequency deviates no more than  $10^{-7}$  from the standard division ratio. To ascertain this requires about 8 s (NTSC). Switching off color-locked operation takes place automatically, in the case of a change of program for example, within approximately 67 ms (e.g. two NTSC fields, 60 Hz).

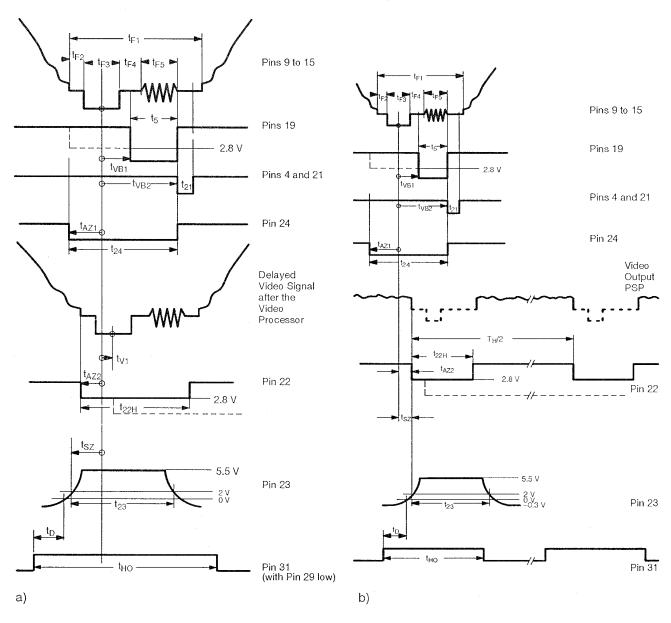

**Table 3–1:** Times relating to Fig. 3–5. The times are given in  $\mu$ s, the values in brackets represent the corresponding numbers of  $\Phi$ M clock periods with SP = 16 and ZM = 1

| Standard                                                                                    | PAL or SECAM with "BP" = 18                       |                          | NTSC with "BP" = 19                              |                           | Text mode with "BP"=18                           |  |

|---------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------|--------------------------------------------------|---------------------------|--------------------------------------------------|--|

|                                                                                             | DPU 2554                                          | DPU 2553                 | DPU 2554                                         | DPU 2553                  | DPU 2553                                         |  |

| One clock period =                                                                          | 56.38 ns                                          | 56.38 ns                 | 69.84 ns                                         | 69.84 ns                  | 56. 38 ns                                        |  |

| t <sub>F1</sub><br>t <sub>F2</sub><br>t <sub>F3</sub><br>t <sub>F4</sub><br>t <sub>F5</sub> | 12.0<br>1.5<br>4.7<br>0.9<br>2.25                 | -<br>-<br>-<br>-         | 10.95<br>1.75<br>4.77<br>min. 0.38<br>min. 2.23  | -<br>-<br>-<br>-          | 10.0<br>0.25<br>3.25<br>-                        |  |

| tvB1<br>t <sub>19L</sub><br>tvB2<br>t <sub>21</sub>                                         | 2.82 (50)<br>3.67 (65)<br>6.49 (115)<br>0.86 (15) |                          | 2.80 (40)<br>3.22 (46)<br>6.02 (86)<br>0.84 (12) | -<br>-<br>-               | 2.26 (40)<br>2.59 (46)<br>7.85 (86)<br>0.86 (15) |  |

| t <sub>AZ1</sub><br>t <sub>24</sub>                                                         | 3.85 (68)<br>10.4 (184)                           |                          | 4.05 (58)<br>10.36 (148)                         | _                         | 3.27 (58)<br>8.34 (148)                          |  |

| t <sub>AZ2</sub><br>t <sub>22H</sub>                                                        | -0.22 (-4)<br>6.2 (110)                           | -0.22 (-4)<br>12.0 (213) | -1.26 (-18)<br>5.75 (82)                         | -1.26 (-18)<br>10.9 (156) | -1.02 (-18)<br>10.04 (178)                       |  |

| t <sub>SZ</sub>                                                                             | -0.22 (-4)                                        | -0.22 (-4)               | -1.54 (-22)                                      | -0.98 (-14)               | -0.79 (-14)                                      |  |

| t <sub>HO min</sub>                                                                         | 1<br>63                                           | 1<br>31                  | 1<br>63                                          | 1<br>31                   | 1<br>63                                          |  |

| t <sub>AS1</sub> and t <sub>AS2</sub>                                                       | 0.79                                              | _                        | 0.98                                             | _                         | 0.79 (14)                                        |  |

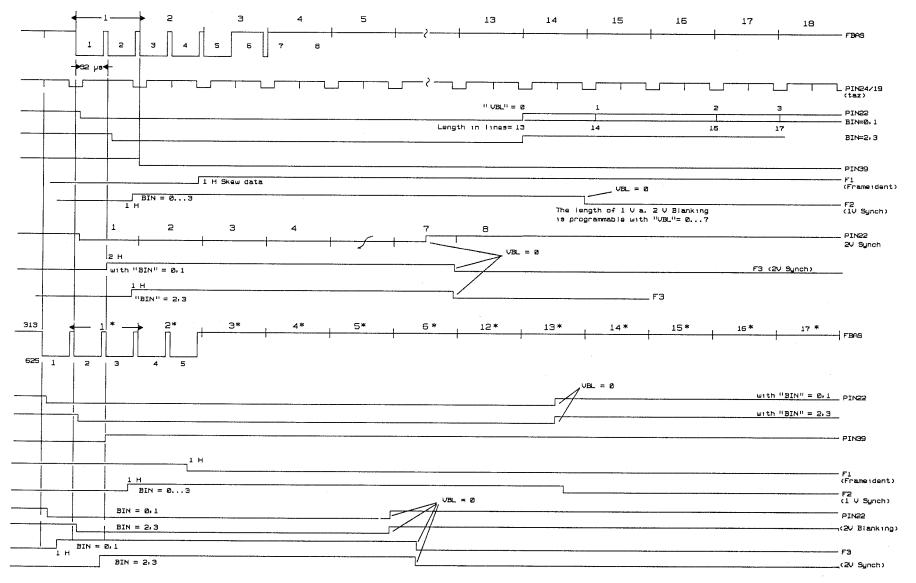

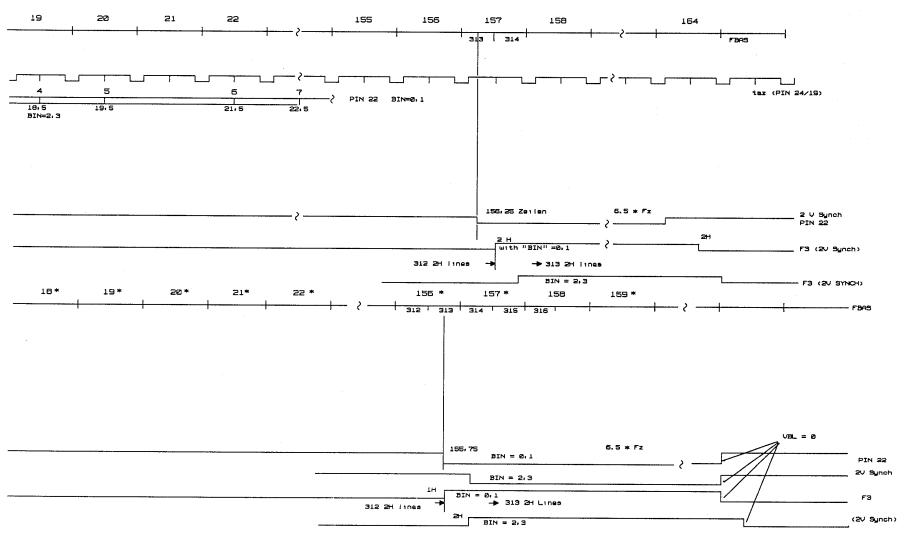

Fig. 3–5: Pulse diagram for the horizontal frequency a) normal standard (DPU 2553) b) double–scan mode (DPU 2554)

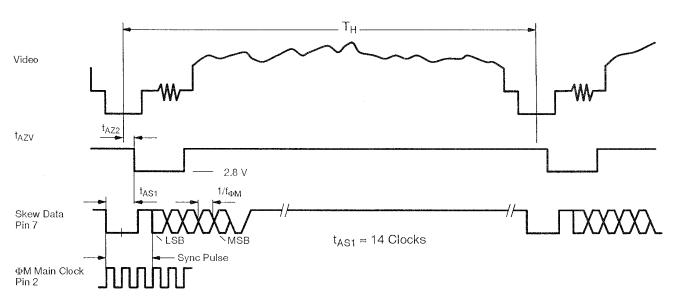

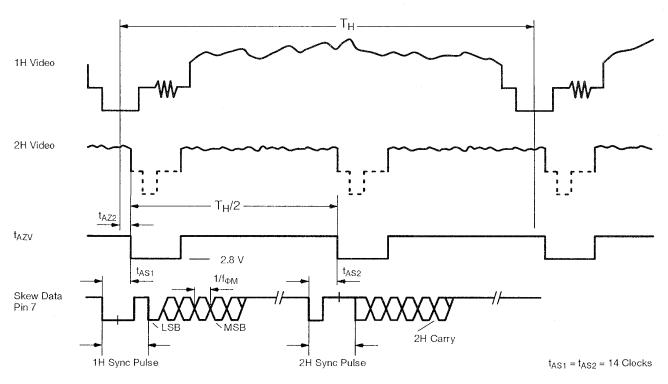

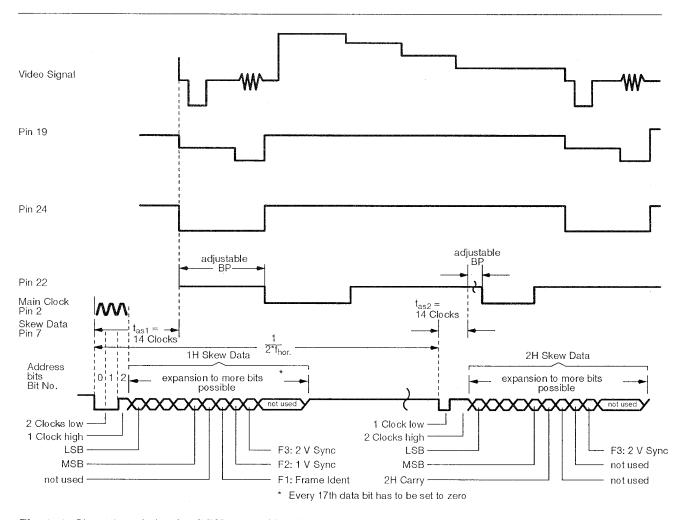

# 3.3.3. Skew Data Output and Field Number Information

With non-standard input signals, the TPU 2735 or TPU 2740 Teletext Processor produce a phase error with respect to the deflection phase.

The DPU generates a digital data stream (skew data, pin 7 of the DPU), which informs the PSP and TPU on the amount of phase delay (given in 2.2 ns increments) used in the DPU for the 1H and 2H output pulse com-

pared with the FM main clock signal of 17.7 MHz (PAL or SECAM) or 14.3 MHz (NTSC), see also Figs. 3–6 to 3–8. The skew data is used by the PSP and by the TPU to adjust the double–scan video signal to the 1H and 2H phase of the horizontal deflection to correct these phase errors.

For the VMC processor the skew data contains three additional bits for information about frame number, 1 V sync and 2 V sync start.

Fig. 3-6: Skew data timing at pin 7 of DPU 2553 with ASK = 1

Fig. 3–7: Skew data timing at pin 7 of DPU 2554 with ASK = 1

Fig. 3–8: Skew data timing for DPU 2554 with ASK = 0

Fig. 3-9: Timing of pin 39 and of the frame-ident data bits

Fig. 3-10: Fig. 3-9 continued

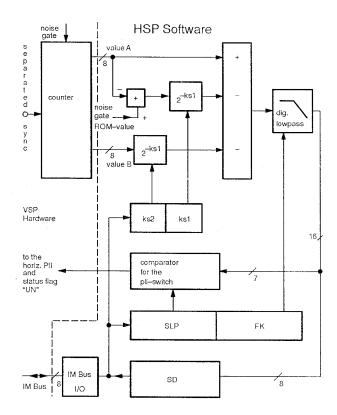

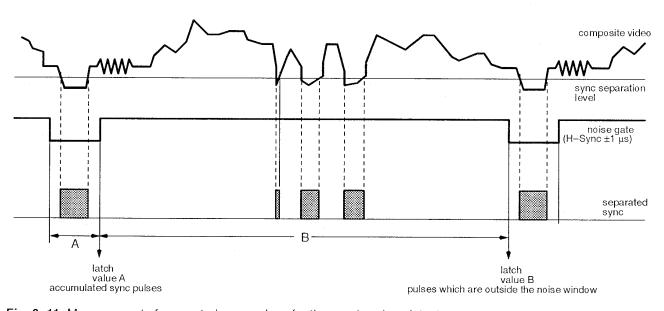

# 3.3.4. Synchronism Detector for PLL and Muting Signal

To evaluate locking of the horizontal PLL and condition of the signal, the DPU's HSP high-speed processor (Fig. 3-1) receives two items of information from the horizontal PLL circuit (see Fig. 3-11).

a) the overall pulsewidth of the separated sync pulses during a  $6.7~\mu s$  phase window centered to the horizontal sync pulse (value A in Fig. 3–11).

b) the overall pulsewidth of the separated sync pulse during one horizontal line but outside the phase window (value B in Fig. 3–11).

Based on a) and b) and using the selectable coefficients KS1 and KS2 and a digital lowpass filter, the HSP processor evaluates an 8-bit item of information "SD" (see Fig. 3-12). By means of a comparator and a selectable level SLP, the switching threshold for the PLL signal "UN" is generated. UN indicates whether the PLL is in the synchronous or in the asynchronous state.

To produce a muting signal in the CCU, the data SD can be read by the CCU. The range of SD extends from 0 (asynchronous) to +127 (synchronous). Typical values for the comparator levels and their hysteresis R1 = 30/20 and for muting 40/30 (see also HSP RAM address Table 5–6).

The corner frequency for the digital lowpass filter in Fig. 3–12 can be selected as shown in Table 3–2.

Table 3-2: Corner frequency of the digital lowpass filter

| fk | Corner Frequency |

|----|------------------|

| 0  | 20 Hz            |

| 1  | 10 Hz            |

| 2  | 5 Hz             |

| 3  | 2.5 Hz           |

Fig. 3-12: Block diagram of the synchronism detector

Fig. 3-11: Measurement of separated sync pulses for the synchronism detector

## 3.4. Start Oscillator and Protection Circuit

To protect the horizontal output stage of the TV set during changing the standard and for using the DPU as a low power start oscillator, an additional oscillator is provided on—chip (Fig. 3—4), with the output connected to pin 31. This oscillator is controlled by a 4 MHz signal independent from the FM main clock produced by the MCU 2600 or MCU 2632 Clock Generator IC and is powered by a separate supply connected to pin 35. The function of this circuitry depends on the external standard selection input pin 33 and on the start oscillator select input pin 36, as described in Table 3—3. Using the protection circuit as a start oscillator, the following operation modes are available (see Table 3—3).

With pin 33 open—circuit, pin 36 at high potential (connected to pin 35) and a 4 MHz clock applied to pin 34, the protection circuit acts as a start oscillator. This produces a constant—frequency horizontal output pulse of 15.5 kHz in the case of DPU 2553, and of 31 kHz in the case of DPU 2554 while the Reset input pin 5 is at low potential. The pulsewidth is 30  $\mu s$  with DPU 2553, and 16  $\mu s$  with DPU 2554. Main clock at pin 2 or main power supplies at pins 8, 32 and 40 are not required for this start oscillator. After the main power supply is stabilized and the main clock generator has started, the Reset input pin 5 most be switched to the high state. As long as the start values from the CCU are invalid, the start oscillator will continuously supply the output pulses of constant frequency to pin 31. By means of the start values given by

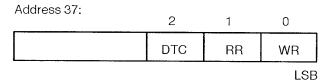

the CCU via the IM bus, the register FL must be set to zero to enable the start oscillator to be triggered by the horizontal PLL circuit. After that, the output frequency and phase are controlled by the horizontal PLL only.