INTEGRATED CIRCUITS

Tentative Device Specification Version: 2.85

2001 Apr 12 Previous date: 2000 Nov 29

Philips Semiconductors

# GENERAL DESCRIPTION

The various versions of theTDA935X/6X/8X PS/N2 series combine the functions of a TV signal processor together with a  $\mu$ -Controller and US Closed Caption decoder. Most versions have a Teletext decoder on board. The Teletext decoder has an internal RAM memory for 1or 10 page text. The ICs are intended to be used in economy television receivers with 90° and 110° picture tubes.

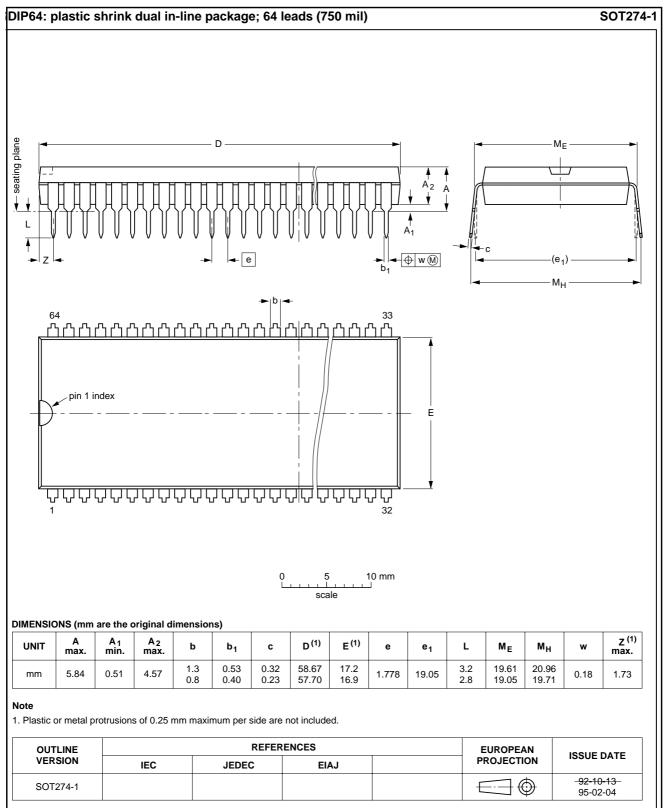

The ICs have supply voltages of 8 V and 3.3 V and they are mounted in S-DIP envelope with 64 pins.

The features are given in the following feature list. The differences between the various ICs are given in the table on page 4.

# TDA935X/6X/8X PS/N2 series

# FEATURES

### **TV-signal processor**

- Multi-standard vision IF circuit with alignment-free PLL demodulator

- Internal (switchable) time-constant for the IF-AGC circuit

- A choice can be made between versions with mono intercarrier sound FM demodulator and versions with QSS IF amplifier.

- The mono intercarrier sound versions have a selective FM-PLL demodulator which can be switched to the different FM sound frequencies (4.5/5.5/6.0/6.5 MHz). The quality of this system is such that the external band-pass filters can be omitted.

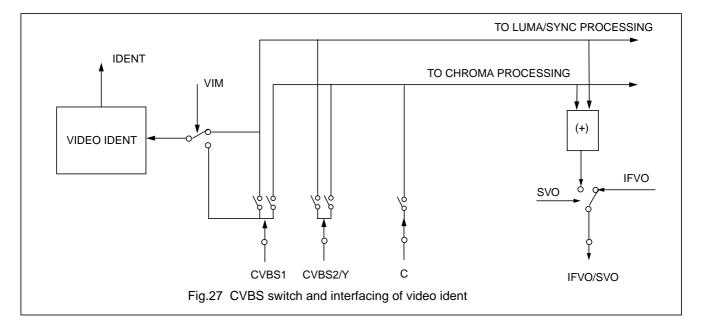

- Source selection between 'internal' CVBS and external CVBS or Y/C signals

- Integrated chrominance trap circuit

- Integrated luminance delay line with adjustable delay time

- Picture improvement features with peaking (with variable centre frequency and positive/negative overshoot ratio) and black stretching

- Integrated chroma band-pass filter with switchable centre frequency

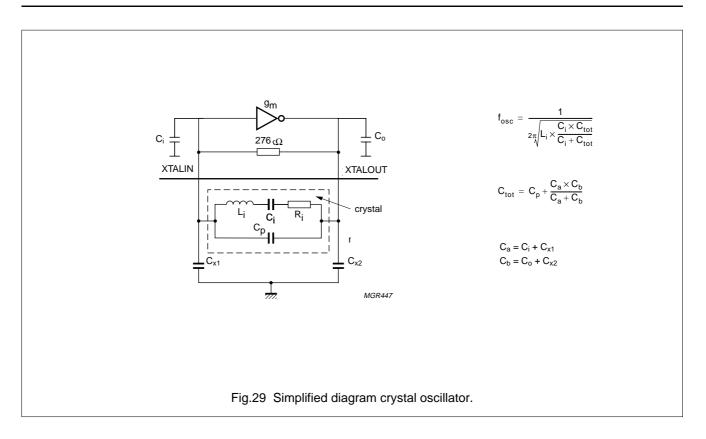

- Only one reference (12 MHz) crystal required for the  $\mu$ -Controller, Teletext- and the colour decoder

- PAL/NTSC or multi-standard colour decoder with automatic search system

- Internal base-band delay line

- RGB control circuit with 'Continuous Cathode Calibration', white point and black level offset adjustment so that the colour temperature of the dark and the light parts of the screen can be chosen independently.

- Linear RGB or YUV input with fast blanking for external RGB/YUV sources. The Text/OSD signals are internally supplied from the μ-Controller/Teletext decoder

- Contrast reduction possibility during mixed-mode of OSD and Text signals

- Horizontal synchronization with two control loops and alignment-free horizontal oscillator

- Vertical count-down circuit

- Vertical driver optimized for DC-coupled vertical output stages

- · Horizontal and vertical geometry processing

- Horizontal and vertical zoom function for 16 : 9 applications

- Horizontal parallelogram and bow correction for large screen picture tubes

- Low-power start-up of the horizontal drive circuit

# μ**-Controller**

- 80C51  $\mu\text{-controller}$  core standard instruction set and timing

- 1 µs machine cycle

- 32 128Kx8-bit late programmed ROM

- 3 12Kx8-bit Auxiliary RAM (shared with Display and Acquisition)

- Interrupt controller for individual enable/disable with two level priority

- Two 16-bit Timer/Counter registers

- One 16 bit Timer with 8-bit Pre-scaler

- WatchDog timer

- Auxiliary RAM page pointer

- 16-bit Data pointer

- Stand-by, Idle and Power Down (PD) mode

- 14 bits PWM for Voltage Synthesis Tuning

- 8-bit A/D converter

- 4 pins which can be programmed as general I/O pin, ADC input or PWM (6-bit) output

# **Data Capture**

- Text memory for 0, 1 or 10 pages

- In the 10 page versions inventory of transmitted Teletext pages stored in the Transmitted Page Table (TPT) and Subtitle Page Table (SPT)

- Data Capture for US Closed Caption

- Data Capture for 525/625 line WST, VPS (PDC system A) and Wide Screen Signalling (WSS) bit decoding

- Automatic selection between 525 WST/625 WST

- Automatic selection between 625 WST/VPS on line 16 of VBI

- Real-time capture and decoding for WST Teletext in Hardware, to enable optimized μ-processor throughput

- Automatic detection of FASTEXT transmission

- Real-time packet 26 engine in Hardware for processing accented, G2 and G3 characters

- Signal quality detector for video and WST/VPS data types

- Comprehensive teletext language coverage

- Full Field and Vertical Blanking Interval (VBI) data capture of WST data

# TDA935X/6X/8X PS/N2 series

# Display

- Teletext and Enhanced OSD modes

- Features of level 1.5 WST and US Close Caption

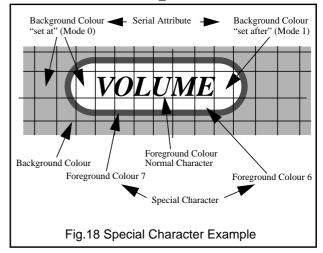

- Serial and Parallel Display Attributes

- Single/Double/Quadruple Width and Height for characters

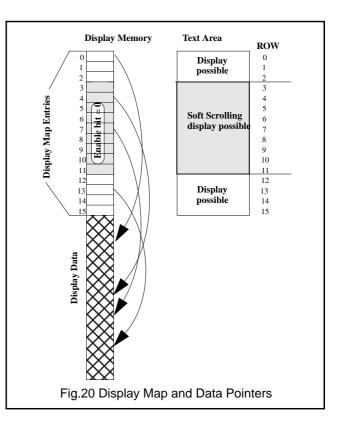

- Scrolling of display region

- Variable flash rate controlled by software

- Enhanced display features including overlining, underlining and italics

- Soft colours using CLUT with 4096 colour palette

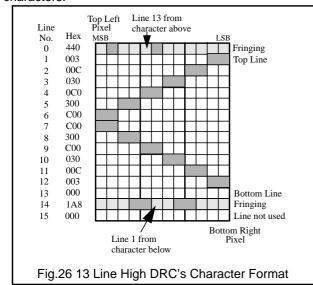

- Globally selectable scan lines per row (9/10/13/16) and character matrix [12x10, 12x13, 12x16 (VxH)]

- Fringing (Shadow) selectable from N-S-E-W direction

- Fringe colour selectable

- · Meshing of defined area

- · Contrast reduction of defined area

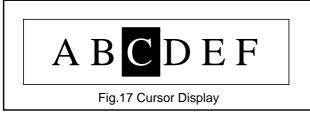

- Cursor

- Special Graphics Characters with two planes, allowing four colours per character

- 32 software redefinable On-Screen display characters

- 4 WST Character sets (G0/G2) in single device (e.g. Latin, Cyrillic, Greek, Arabic)

- G1 Mosaic graphics, Limited G3 Line drawing characters

- WST Character sets and Closed Caption Character set in single device

# Tentative Device Specification

# embedded µ-Controller TV signal processor-Teletext decoder with

# TDA935X/6X/8X PS/N2 series

| IC VERSION (TDA)                                                                                          | 9350        | 9351                          | 9352        | 9353         | 9360         | 9361         | 9362        | 9363         | 9364         | 9365         | 9366        | 9367         | 9380         | 9381        | 9382         | 9383         | 9384        | 9385         | 9386         | 9387         | 9388        | 938      |

|-----------------------------------------------------------------------------------------------------------|-------------|-------------------------------|-------------|--------------|--------------|--------------|-------------|--------------|--------------|--------------|-------------|--------------|--------------|-------------|--------------|--------------|-------------|--------------|--------------|--------------|-------------|----------|

| TV range                                                                                                  | 90°         | 90°                           | 90°         | 110°         | 90°          | 90°          | 110°        | 110°         | 110°         | 110°         | 90°         | 90°          | 90°          | 90°         | 90°          | 110°         | 110°        | 110°         | 110°         | 90°          | 110°        | 110      |

| Mono intercarrier multi-standard<br>sound demodulator (4.5 - 6.5 MHz)<br>with switchable centre frequency | V           | V                             |             | V            | $\checkmark$ | $\checkmark$ | V           | $\checkmark$ |              |              |             |              | $\checkmark$ | V           |              | $\checkmark$ | V           |              |              | V            | V           |          |

| Audio switch                                                                                              |             |                               |             | $\checkmark$ | $\checkmark$ |              |             | $\checkmark$ |              |              |             |              | $\checkmark$ |             |              |              |             |              |              | $\checkmark$ |             |          |

| Automatic Volume Levelling                                                                                |             |                               |             |              | $\checkmark$ |              |             |              |              |              |             |              | $\checkmark$ |             |              |              |             |              |              | $\checkmark$ | [           |          |

| Automatic Volume Levelling <b>or</b><br>subcarrier output (for comb filter<br>applications)               |             |                               |             | V            |              |              | V           | $\checkmark$ |              | $\checkmark$ |             |              |              |             |              | $\checkmark$ | V           | V            | V            |              | V           | ٧        |

| QSS sound IF amplifier with<br>separate input and AGC circuit                                             |             |                               | V           |              |              |              |             |              | $\checkmark$ | $\checkmark$ | V           | $\checkmark$ |              |             | $\checkmark$ |              |             | V            | $\checkmark$ |              |             | 1        |

| AM sound demodulator without extra reference circuit                                                      |             |                               |             |              |              |              |             |              |              |              |             |              |              |             |              |              |             |              |              |              |             |          |

| PAL decoder                                                                                               |             |                               |             | $\checkmark$ | $\checkmark$ |              |             | $\checkmark$ |              | $\checkmark$ |             | $\checkmark$ | $\checkmark$ |             |              |              |             | $\checkmark$ |              |              |             |          |

| SECAM decoder                                                                                             |             |                               |             | $\checkmark$ |              |              |             | $\checkmark$ |              | $\checkmark$ |             | $\checkmark$ |              |             |              |              |             |              |              |              |             |          |

| NTSC decoder                                                                                              |             |                               |             | $\checkmark$ | $\checkmark$ |              |             | $\checkmark$ |              | $\checkmark$ |             |              | $\checkmark$ |             |              |              |             | $\checkmark$ |              | $\checkmark$ |             | ٦        |

| Horizontal geometry (E-W)                                                                                 |             |                               |             | $\checkmark$ |              |              |             | $\checkmark$ | $\checkmark$ | $\checkmark$ |             |              |              |             |              | $\checkmark$ |             | $\checkmark$ |              |              |             | N        |

| Horizontal and Vertical Zoom                                                                              |             |                               |             | $\checkmark$ |              |              |             | $\checkmark$ |              | $\checkmark$ |             |              |              |             |              | $\checkmark$ |             | $\checkmark$ |              |              |             | N        |

| ROM size                                                                                                  | 32-<br>64 k | 32-<br>64 k                   | 32-<br>64 k | 32-<br>64 k  | 64-<br>128k  | 64-<br>128k  | 64-<br>128k | 64-<br>128k  | 64-<br>128k  | 64-<br>128k  | 64-<br>128k | 64-<br>128k  | 16-<br>64 k  | 16-<br>64 k | 16-<br>64 k  | 16-<br>64 k  | 16-<br>64 k | 16-<br>64 k  | 16-<br>64 k  | 16-<br>64 k  | 16-<br>64 k | 16<br>64 |

| User RAM size                                                                                             | 1 k         | 1 k                           | 1 k         | 1 k          | 2 k          | 2 k          | 2 k         | 2 k          | 2 k          | 2 k          | 2 k         | 2 k          | 1 k          | 1 k         | 1 k          | 1 k          | 1 k         | 1 k          | 1 k          | 1 k          | 1 k         | 1        |

| Teletext                                                                                                  | 1<br>page   | 1<br>page                     | 1<br>page   | 1<br>page    | 10<br>page   | 10<br>page   | 10<br>page  | 10<br>page   | 10<br>page   | 10<br>page   | 10<br>page  | 10<br>page   |              |             |              |              |             |              |              |              |             |          |

| Closed captioning                                                                                         | √           | , <u>⊸</u> , <sub>0</sub> , - | √           | 1            | √            | √<br>√       | √<br>√      | 1            | √<br>√       | √            | 1           | √            |              |             | 2            |              |             |              |              |              |             |          |

Philips Semiconductors

# TDA935X/6X/8X PS/N2 series

# QUICK REFERENCE DATA

| SYMBOL                     | PARAMETER                                                               | MIN. | TYP.      | MAX. | UNIT |

|----------------------------|-------------------------------------------------------------------------|------|-----------|------|------|

| Supply                     |                                                                         | -    | L.        |      | -!   |

| V <sub>P</sub>             | supply voltages                                                         | -    | 8.0/3.3   | -    | V    |

| I <sub>P</sub>             | supply current                                                          | -    | 135/60    | -    | mA   |

| Input voltage              | S                                                                       |      |           |      | 1    |

| V <sub>iVIFrms</sub> )     | video IF amplifier sensitivity (RMS value)                              | -    | 75        | -    | μV   |

| V <sub>iSIF(rms)</sub>     | QSS sound IF amplifier sensitivity (RMS value)                          | -    | 60        | -    | μV   |

| V <sub>iAUDIO(rms)</sub>   | external audio input (RMS value)                                        | -    | 500       | -    | mV   |

| V <sub>iCVBS(p-p)</sub>    | external CVBS/Y input (peak-to-peak value)                              | -    | 1.0       | -    | V    |

| V <sub>iCHROMA(p-p)</sub>  | external chroma input voltage (burst amplitude)<br>(peak-to-peak value) | -    | 0.3       | -    | V    |

| V <sub>iRGB(p-p)</sub>     | RGB inputs (peak-to-peak value)                                         | -    | 0.7       | -    | V    |

| V <sub>iYIN(p-p)</sub>     | luminance input signal (peak-to-peak value)                             | -    | 1.4       | -    | V    |

| V <sub>iUVIN(p-p)</sub>    | U/V input signal (peak-to-peak value)                                   | -    | 1.33/1.05 | -    | V    |

| Output signal              | ls                                                                      |      |           |      |      |

| V <sub>o(IFVO)(p-p)</sub>  | demodulated CVBS output (peak-to-peak value)                            | _    | 2.5       | _    | V    |

| V <sub>o(QSSO)(rms)</sub>  | sound IF intercarrier output in QSS versions (RMS value)                | -    | 100       | -    | mV   |

| V <sub>o(AMOUT)(rms)</sub> | demodulated AM sound output in QSS versions (RMS value)                 | _    | 500       | -    | mV   |

| I <sub>o(AGCOUT)</sub>     | tuner AGC output current range                                          | 0    | _         | 5    | mA   |

| V <sub>oRGB(p-p)</sub>     | RGB output signal amplitudes (peak-to-peak value)                       | -    | 2.0       | -    | V    |

| I <sub>₀HOUT</sub>         | horizontal output current                                               | 10   | _         | _    | mA   |

| I <sub>overt</sub>         | vertical output current (peak-to-peak value)                            | 1    | _         | _    | mA   |

| I <sub>oEWD</sub>          | EW drive output current                                                 | 1.2  | -         | -    | mA   |

# TDA935X/6X/8X PS/N2 series

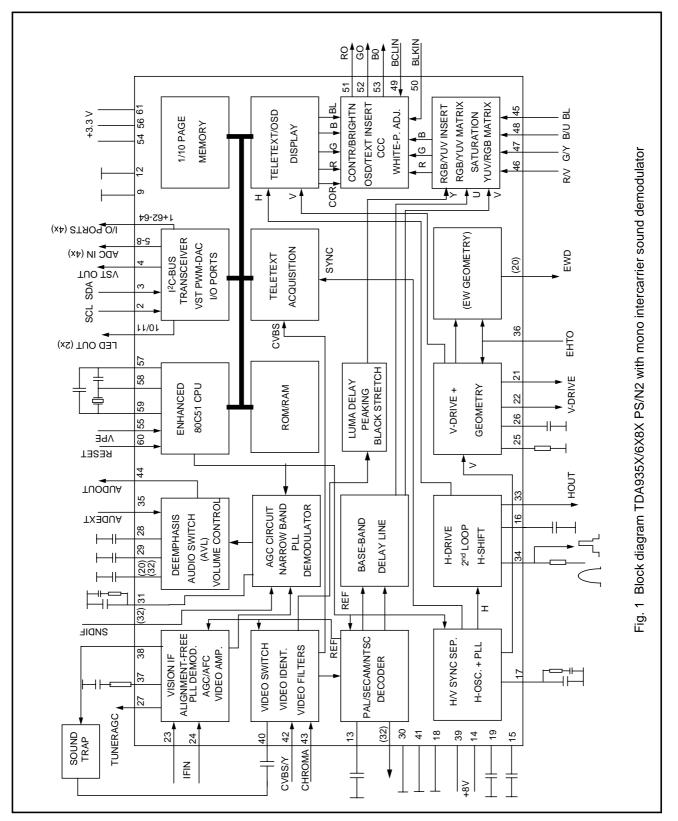

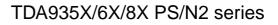

# **BLOCK DIAGRAM**

# TDA935X/6X/8X PS/N2 series

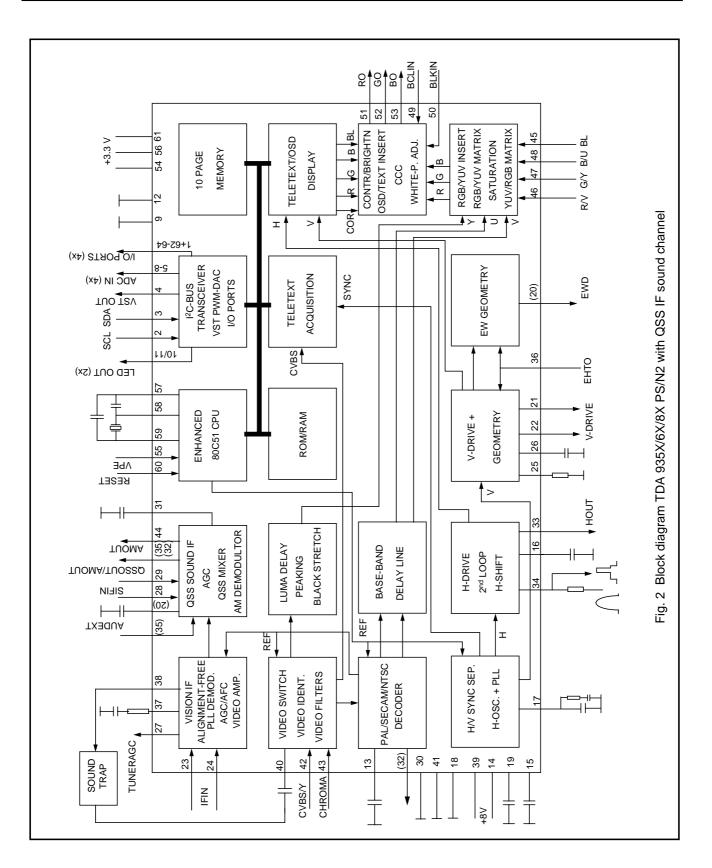

# PINNING

| SYMBOL                        | PIN | DESCRIPTION                                                                          |

|-------------------------------|-----|--------------------------------------------------------------------------------------|

| P1.3/T1                       | 1   | port 1.3 or Counter/Timer 1 input                                                    |

| P1.6/SCL                      | 2   | port 1.6 or I <sup>2</sup> C-bus clock line                                          |

| P1.7/SDA                      | 3   | port 1.7 or I <sup>2</sup> C-bus data line                                           |

| P2.0/TPWM                     | 4   | port 2.0 or Tuning PWM output                                                        |

| P3.0/ADC0                     | 5   | port 3.0 or ADC0 input                                                               |

| P3.1/ADC1                     | 6   | port 3.1 or ADC1 input                                                               |

| P3.2/ADC2                     | 7   | port 3.2 or ADC2 input                                                               |

| P3.3/ADC3                     | 8   | port 3.3 or ADC3 input                                                               |

| VSSC/P                        | 9   | digital ground for μ-Controller core and periphery                                   |

| P0.5                          | 10  | port 0.5 (8 mA current sinking capability for direct drive of LEDs)                  |

| P0.6                          | 11  | port 0.6 (8 mA current sinking capability for direct drive of LEDs)                  |

| VSSA                          | 12  | analog ground of Teletext decoder and digital ground of TV-processor                 |

| SECPLL                        | 13  | SECAM PLL decoupling                                                                 |

| VP2                           | 14  | 2 <sup>nd</sup> supply voltage TV-processor (+8V)                                    |

| DECDIG                        | 15  | decoupling digital supply of TV-processor                                            |

| PH2LF                         | 16  | phase-2 filter                                                                       |

| PH1LF                         | 17  | phase-1 filter                                                                       |

| GND3                          | 18  | ground 3 for TV-processor                                                            |

| DECBG                         | 19  | bandgap decoupling                                                                   |

| AVL/EWD <sup>(1)</sup>        | 20  | Automatic Volume Levelling /East-West drive output                                   |

| VDRB                          | 21  | vertical drive B output                                                              |

| VDRA                          | 22  | vertical drive A output                                                              |

| IFIN1                         | 23  | IF input 1                                                                           |

| IFIN2                         | 24  | IF input 2                                                                           |

| IREF                          | 25  | reference current input                                                              |

| VSC                           | 26  | vertical sawtooth capacitor                                                          |

| TUNERAGC                      | 27  | tuner AGC output                                                                     |

| AUDEEM/SIFIN1 <sup>(1)</sup>  | 28  | audio deemphasis or SIF input 1                                                      |

| DECSDEM/SIFIN2 <sup>(1)</sup> | 20  | decoupling sound demodulator or SIF input 2                                          |

| GND2                          | 30  | ground 2 for TV processor                                                            |

| SNDPLL/SIFAGC <sup>(1)</sup>  | 31  | narrow band PLL filter /AGC sound IF                                                 |

| AVL/SNDIF/REF0/               | 32  | Automatic Volume Levelling / sound IF input / subcarrier reference output /AM output |

| AMOUT <sup>(1)</sup>          | 52  | (non controlled)                                                                     |

| HOUT                          | 33  | horizontal output                                                                    |

| FBISO                         | 34  | flyback input/sandcastle output                                                      |

| AUDEXT/                       | 35  | external audio input /QSS intercarrier out /AM audio output (non controlled)         |

| QSSO/AMOUT <sup>(1)</sup>     |     |                                                                                      |

| EHTO                          | 36  | EHT/overvoltage protection input                                                     |

| PLLIF                         | 37  | IF-PLL loop filter                                                                   |

| IFVO/SVO                      | 38  | IF video output / selected CVBS output                                               |

| VP1                           | 39  | main supply voltage TV-processor (+8 V)                                              |

| CVBSINT                       | 40  | internal CVBS input                                                                  |

| GND1                          | 40  | ground 1 for TV-processor                                                            |

| CVBS/Y                        | 41  | external CVBS/Y input                                                                |

| CHROMA                        | 42  | chrominance input (SVHS)                                                             |

|                               |     | audio output /AM audio output (volume controlled)                                    |

|                               | 44  | audio output /Aivi audio output (volume controlled)                                  |

# TDA935X/6X/8X PS/N2 series

| SYMBOL    | PIN | DESCRIPTION                                                                  |

|-----------|-----|------------------------------------------------------------------------------|

| INSSW2    | 45  | 2 <sup>nd</sup> RGB / YUV insertion input                                    |

| R2/VIN    | 46  | 2 <sup>nd</sup> R input / V (R-Y) input                                      |

| G2/YIN    | 47  | 2 <sup>nd</sup> G input / Y input                                            |

| B2/UIN    | 48  | 2 <sup>nd</sup> B input / U (B-Y) input                                      |

| BCLIN     | 49  | beam current limiter input / (V-guard input, note 2)                         |

| BLKIN     | 50  | black current input / (V-guard input, note 2)                                |

| RO        | 51  | Red output                                                                   |

| GO        | 52  | Green output                                                                 |

| BO        | 53  | Blue output                                                                  |

| VDDA      | 54  | analog supply of Teletext decoder and digital supply of TV-processor (3.3 V) |

| VPE       | 55  | OTP Programming Voltage                                                      |

| VDDC      | 56  | digital supply to core (3.3 V)                                               |

| OSCGND    | 57  | oscillator ground supply                                                     |

| XTALIN    | 58  | crystal oscillator input                                                     |

| XTALOUT   | 59  | crystal oscillator output                                                    |

| RESET     | 60  | reset                                                                        |

| VDDP      | 61  | digital supply to periphery (+3.3 V)                                         |

| P1.0/INT1 | 62  | port 1.0 or external interrupt 1 input                                       |

| P1.1/T0   | 63  | port 1.1 or Counter/Timer 0 input                                            |

| P1.2/INT0 | 64  | port 1.2 or external interrupt 0 input                                       |

Note

- The function of pin 20, 28, 29, 31, 32, 35 and 44 is dependent on the IC version (mono intercarrier FM demodulator /QSS IF amplifier and East-West output or not) and on some software control bits. The valid combinations are given in table 1.

- 2. The vertical guard function can be controlled via pin 49 or pin 50. The selection is made by means of the IVG bit in subaddress 2BH.

| IC version     |                      | FM-P                | LL version               |                     |                                   |     | QSS v             | ersion      |       |                   |  |  |

|----------------|----------------------|---------------------|--------------------------|---------------------|-----------------------------------|-----|-------------------|-------------|-------|-------------------|--|--|

| East-West Y/N  | I                    | N                   | Y                        |                     |                                   | Ν   |                   |             | Y     |                   |  |  |

| CMB1/CMB0 bits | 00                   | 01/10/11            | 00                       | 01/10/11            | 00                                | 01/ | 10/11             | 00          | 01/   | 10/11             |  |  |

| AM bit         | _                    | -                   | _                        | _                   | _                                 | 0   | 1                 | _           | - 0 1 |                   |  |  |

| Pin 20         | A                    | VL                  | EWD                      | )                   |                                   | AVL |                   |             | EWD   |                   |  |  |

| Pin 28         |                      | A                   | JDEEM                    |                     |                                   |     | SIF               | IN1         |       |                   |  |  |

| Pin 29         |                      | DE                  | CSDEM                    |                     | SIFIN2                            |     |                   |             |       |                   |  |  |

| Pin 31         |                      | S                   | NDPLL                    |                     |                                   |     | SIF               | AGC         |       |                   |  |  |

| Pin 32         | SNDIF <sup>(1)</sup> | REFO <sup>(2)</sup> | AVL/SNDIF <sup>(1)</sup> | REFO <sup>(2)</sup> | AMOUT                             | RE  | FO <sup>(2)</sup> | AMOUT       | RE    | FO <sup>(2)</sup> |  |  |

| Pin 35         |                      | A                   | UDEXT                    |                     | AUDEXT QSSO AMOUT AUDEXT QSSO AMO |     |                   |             |       | AMOUT             |  |  |

| Pin 44         |                      | А                   | UDOUT                    |                     |                                   | con | trolled AN        | /l or audio | out   |                   |  |  |

# Table 1 Pin functions for various versions

# Note

1. When additional (external) selectivity is required for FM-PLL system pin 32 can be used as sound IF input. This function is selected by means of SIF bit in subaddress 28H.

2. The reference output signal is only available for the CMB1/CMB0 setting of 0/1. For the other settings this pin is a switch output (see also table 67).

# TDA935X/6X/8X PS/N2 series

| -                        |      |                     |        |                       |

|--------------------------|------|---------------------|--------|-----------------------|

|                          |      |                     |        |                       |

| P1.3/T1                  | 1    | U                   | 64     | P1.2/INT0             |

| P1.6/SCL                 | 2    |                     | 63     | P1.1/T0               |

| P1.7/SDA                 | 3    |                     | 62     | P1.0/INT1             |

| P2.0/TPMW                | 4    |                     | 61     | VDDP                  |

| P3.0/ADC0                | 5    |                     | 60     | RESET                 |

| P3.1/ADC1                | 6    |                     | 59     | XTALOUT               |

| P3.2/ADC2                | 7    |                     | 58     | XTALIN                |

| P3.3/ADC3                | 8    |                     | 57     | OSCGND                |

| VSSC/P                   | 9    |                     | 56     | VDDC                  |

| P0.5                     | 10   | 7                   | 55     | VPE                   |

| P0.6                     | 11   | TDA935X/6X/8X PS/N2 | 54     | VDDA                  |

| VSSA                     | 12   | ă                   | 53     | BO                    |

| SECPLL                   | 13   | (8)                 | 52     | GO                    |

| VP2                      | 14   | (9)                 | 51     | RO                    |

| DECDIG                   | 15   | 35)                 | 50     | BLKIN                 |

| PH2LF                    | 16   | A9                  | 49     | BCLIN                 |

| PH1LF                    | 17   | <b>P</b>            | 48     | B2/UIN                |

| GND3                     | 18   |                     | 47     | G2/YIN                |

| DECBG                    | 19   |                     | 46     | R2/VIN                |

| AVL/EWD                  | 20   |                     | 45     | INSSW2                |

| VDRB                     | 21   |                     | 44     | AUDOUT/AMOUT          |

| VDRA                     | 22   |                     | 43     | CHROMA                |

| IFIN1                    | 23   |                     | 42     | CVBS/Y                |

| IFIN2                    | 24   |                     | 41     | GND1                  |

| IREF                     | 25   |                     | 40     | CVBSINT               |

| VSC                      | 26   |                     | 39     | VP1                   |

| TUNERAGC                 | 27   |                     | 38     | IFVO/SVO              |

| AUDEEM/SIFIN1            | 28   |                     | 37     | PLLIF                 |

| DECSDEM/SIFIN            | 2 29 |                     | 36     | EHTO                  |

| GND2                     | 30   |                     | 35     | AUDEXT/QSSO/<br>AMOUT |

| SNDPLL/SIFAGC            | 31   |                     | 34     | FBISO                 |

| AVL/SNDIF/<br>REFO/AMOUT | 32   |                     | 33     | HOUT                  |

|                          |      | MXXxx               | x      |                       |

| Fig. 3                   | Pin  | configuratio        | on (SI | DIP 64)               |

# FUNCTIONAL DESCRIPTION OF THE 80C51

The functionality of the micro-controller used on this device is described here with reference to the industry standard 80C51 micro-controller. A full description of its functionality can be found in the 80C51 based 8-bit micro-controllers - Philips Semiconductors (ref. IC20).

### Features of the 80c51

- 80C51 micro-controller core standard instruction set and timing.

- 1µs machine cycle.

- Maximum 128K x 8-bit Program ROM.

- Maximum of 12K x 8-bit Auxiliary RAM.

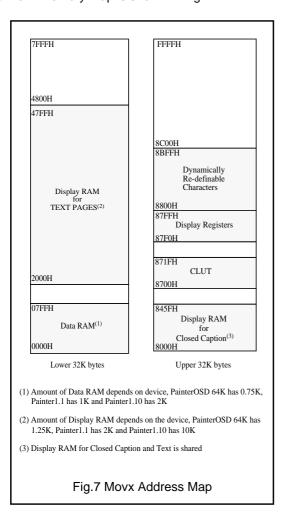

- 2K (OSD only version) Auxiliary RAM, maximum of 1.25K required for Display

- 3K (1 page teletext version) Auxiliary RAM, maximum of 2K required for Display

- 12K (10 page teletext version) Auxiliary RAM, maximum of 10K required for Display

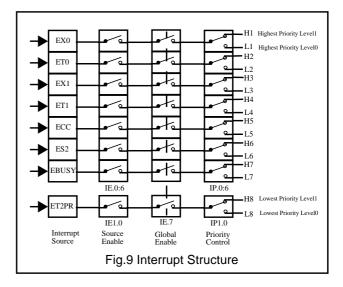

- 8-Level Interrupt Controller for individual enable/disable with two level priority.

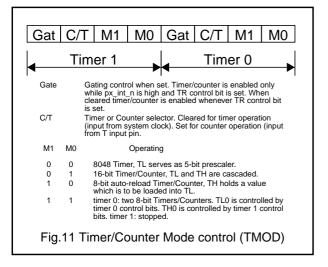

- Two 16-bit Timer/Counters.

- Additional 16-bit Timer with 8-bit Pre-scaler.

- · WatchDog Timer.

- Auxiliary RAM Page Pointer.

- 16-bit Data pointer

- Idle, Stand-by and Power-Down modes.

- 13 General I/O.

- Four 6-bit Pulse Width Modulator (PWM) outputs for control of TV analogue signals.

- One 14-bit PWM for Voltage Synthesis tuner control.

- 8-bit ADC with 4 multiplexed inputs.

- 2 high current outputs for directly driving LED's etc.

- I<sup>2</sup>C Byte Level bus interface.

# **Memory Organisation**

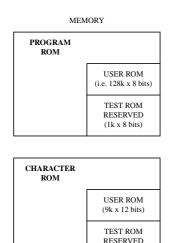

The device has the capability of a maximum of 128K Bytes of PROGRAM ROM and 12K Bytes of DATA RAM. The OSD (& Closed Caption) only version has a 2K RAM and a maximum of 64K ROM, the 1 page teletext version has a 3K RAM and also a maximum of 64K ROM whilst the 10 page teletext version has a 12K RAM and a maximum of 128K ROM.

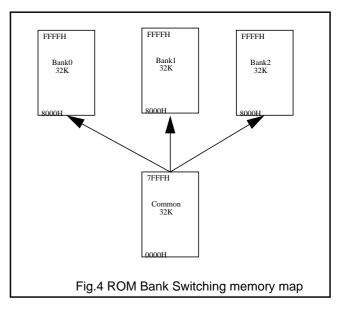

### **ROM Organisation**

The 64K device has a continuous address space from 0 to 64K. The 128K is arranged in four banks of 32K. One of

# TDA935X/6X/8X PS/N2 series

the 32K banks is common and is always addressable. The other three banks (Bank0, Bank1, Bank2) can be accessed by selecting the right bank via the SFR ROMBK bits 1/0.

### **RAM Organisation**

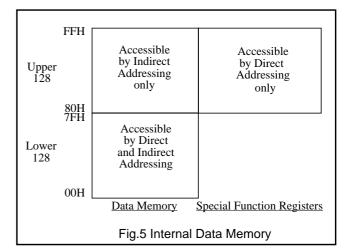

The Internal Data RAM is organised into two areas, Data Memory and Special Function Registers (SFRs) as shown in Fig.5.

### DATA MEMORY

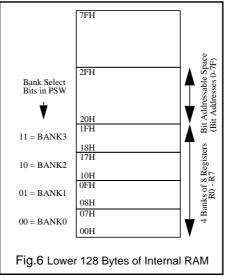

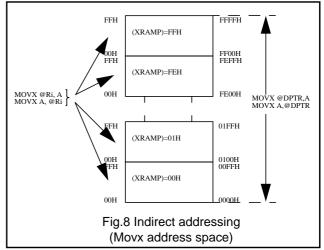

The Data memory is 256 x 8-bits and occupies the address range 00 to FF Hex when using Indirect addressing and 00 to 7F Hex when using direct addressing. The SFRs occupy the address range 80 Hex to FF Hex and are accessible using Direct addressing only. The lower 128 Bytes of Data memory are mapped as shown in Fig.6. The lowest 32

# TDA935X/6X/8X PS/N2 series

bytes are grouped into 4 banks of 8 registers, the next 16 bytes above the register banks form a block of bit addressable memory space. The upper 128 bytes are not allocated for any special area or functions.

# SFR MEMORY

The Special Function Register (SFR) space is used for port latches, counters/timers, peripheral control, data capture and display. These registers can only be accessed by direct addressing. Sixteen of the addresses in the SFR space are both bit and byte addressable. The bit addressable SFRs are those whose address ends in 0H or 8H. A summary of the SFR map in address order is shown in Table 2.

| ADD | R/W | Names | BIT7     | BIT6             | BIT5     | BIT4     | BIT3     | BIT2             | BIT1     | BIT0     |

|-----|-----|-------|----------|------------------|----------|----------|----------|------------------|----------|----------|

| 80H | R/W | P0    | Reserved | P0<6>            | P0<5>    | Reserved | Reserved | Reserved         | Reserved | Reserved |

| 81H | R/W | SP    | SP<7>    | SP<6>            | SP<5>    | SP<4>    | SP<3>    | SP<2>            | SP<1>    | SP<0>    |

| 82H | R/W | DPL   | DPL<7>   | DPL<6>           | DPL<5>   | DPL<4>   | DPL<3>   | DPL<2>           | DPL<1>   | DPL<0>   |

| 83H | R/W | DPH   | DPH<7>   | DPH<6>           | DPH<5>   | DPH<4>   | DPH<3>   | DPH<2>           | DPH<1>   | DPH<0>   |

| 84H | R/W | IEN1  | -        | -                | -        | -        | -        | -                | -        | ET2      |

| 85H | R/W | IP1   | -        | -                | -        | -        | -        | -                | -        | PT2      |

| 87H | R/W | PCON  | 0        | ARD              | RFI      | WLE      | GF1      | GF0              | PD       | IDL      |

| 88H | R/W | TCON  | TF1      | TR1              | TF0      | TR0      | IE1      | IT1              | IE0      | IT0      |

| 89H | R/W | TMOD  | GATE     | $C/\overline{T}$ | M1       | M0       | GATE     | $C/\overline{T}$ | M1       | M0       |

| 8AH | R/W | TL0   | TL0<7>   | TL0<6>           | TL0<5>   | TL0<4>   | TL0<3>   | TL0<2>           | TL0<1>   | TL0<0>   |

| 8BH | R/W | TL1   | TL1<7>   | TL1<6>           | TL1<5>   | TL1<4>   | TL1<3>   | TL1<2>           | TL1<1>   | TL1<0>   |

| 8CH | R/W | тно   | TH0<7>   | TH0<6>           | TH0<5>   | TH0<4>   | TH0<3>   | TH0<2>           | TH0<1>   | TH0<0>   |

| 8DH | R/W | TH1   | TH1<7>   | TH1<6>           | TH1<5>   | TH1<4>   | TH1<3>   | TH1<2>           | TH1<1>   | TH1<0>   |

| 90H | R/W | P1    | P1<7>    | P1<6>            | Reserved | Reserved | P1<3>    | P1<2>            | P1<1>    | P1<0>    |

| 91H | R/W | TP2L  | TP2L<7>  | TP2L<6>          | TP2L<5>  | TP2L<4>  | TP2L<3>  | TP2L<2>          | TP2L<1>  | TP2L<0>  |

Table 2 SFR Map

# TDA935X/6X/8X PS/N2 series

| ADD | R/W | Names  | BIT7                | BIT6             | BIT5            | BIT4                      | BIT3                          | BIT2             | BIT1             | BIT0             |

|-----|-----|--------|---------------------|------------------|-----------------|---------------------------|-------------------------------|------------------|------------------|------------------|

| 92H | R/W | ТР2Н   | TP2H<15>            | TP2H<14>         | TP2H<13>        | TP2H<12>                  | TP2H<11>                      | TP2H<10>         | TP2H<9>          | TP2H<8>          |

| 93H | R/W | TP2PR  | TP2PR<7>            | TP2PR<6>         | TP2PR<5>        | TP2PR<4>                  | TP2PR<3>                      | TP2PR<2>         | TP2PR<1>         | TP2PR<0>         |

| 94H | R/W | TP2CRL | -                   | -                | -               | -                         | -                             | -                | TP2CRL<1>        | TP2CRL<0>        |

| 96H | R/W | P0CFGA | Reserved            | P0CFGA<6>        | P0CFGA<5>       | Reserved                  | Reserved                      | Reserved         | Reserved         | Reserved         |

| 97H | R/W | P0CFGB | Reserved            | P0CFGB<6>        | P0CFGB<5>       | Reserved                  | Reserved                      | Reserved         | Reserved         | Reserved         |

| 98H | R/W | SADB   | -                   | -                | -               | DC_COMP                   | SAD<3>                        | SAD<2>           | SAD<1>           | SAD<0>           |

| 9CH | R   | TP2CL  | TP2CL<7>            | TP2CL<6>         | TP2CL<5>        | TP2CL<4>                  | TP2CL<3>                      | TP2CL<2>         | TP2CL<1>         | TP2CL<0>         |

| 9DH | R   | ТР2СН  | TP2CH<7>            | TP2CH<6>         | TP2CH<5>        | TP2CH<4>                  | TP2CH<3>                      | TP2CH<2>         | TP2CH<1>         | TP2CH<0>         |

| 9EH | R/W | P1CFGA | P1CFGA<7>           | P1CFGA<6>        | Reserved        | Reserved                  | P1CFGA<3>                     | P1CFGA<2>        | P1CFGA<1>        | P1CFGA<0>        |

| 9FH | R/W | P1CFGB | P1CFGB<7>           | P1CFGB<6>        | Reserved        | Reserved                  | P1CFGB<3>                     | P1CFGB<2>        | P1CFGB<1>        | P1CFGB<0>        |

| A0H | R/W | P2     | Reserved            | -                | -               | -                         | -                             | -                | -                | P2<0>            |

| A6H | R/W | P2CFGA | Reserved            | P2CFGA<6>        | P2CFGA<5>       | P2CFGA<4>                 | P2CFGA<3>                     | P2CFGA<2>        | P2CFGA<1>        | P2CFGA<0>        |

| A7H | R/W | P2CFGB | Reserved            | P2CFGB<6>        | P2CFGB<5>       | P2CFGB<4>                 | P2CFGB<3>                     | P2CFGB<2>        | P2CFGB<1>        | P2CFGB<0>        |

| A8H | R/W | IE     | EA                  | EBUSY            | ES2             | ECC                       | ET1                           | EX1              | ET0              | EX0              |

| B0H | R/W | P3     | Reserved            | Reserved         | Reserved        | Reserved                  | P3<3>                         | P3<2>            | P3<1>            | P3<0>            |

| B2H | R/W | TXT18  | NOT<3>              | NOT<2>           | NOT<1>          | NOT<0>                    | 0                             | 0                | BS<1>            | BS<0>            |

| B3H | R/W | TXT19  | TEN                 | TC<2>            | TC<1>           | TC<0>                     | 0                             | 0                | TS<1>            | TS<0>            |

| B4H | R/W | TXT20  | DRCS<br>ENABLE      | OSD<br>PLANES    | 0               | 0                         | OSD LANG<br>ENABLE            | OSD<br>LAN<2>    | OSD<br>LAN<1>    | OSD<br>LAN<0>    |

| B5H | R/W | TXT21  | DISP<br>LINE<1>     | DISP<br>LINES<0> | CHAR<br>SIZE<1> | CHAR<br>SIZE<0>           | Reserved                      | CC ON            | I2C PORT0        | CC/TXT           |

| B6H | R   | TXT22  | GPF1<7>             | GPF1<6>          | GPF1<5>         | GPF1<4>                   | GPF1<3>                       | GPF1<2>          | GPF1<1>          | GPF1<0>          |

| B7H | R/W | CCLIN  | 0                   | 0                | 0               | CS<4>                     | CS<3>                         | CS<2>            | CS<1>            | CS<0>            |

| B8H | R/W | IP     | 0                   | PBUSY            | PES2            | PCC                       | PT1                           | PX1              | PT0              | PX0              |

| B9H | R/W | TXT17  | 0                   | FORCE<br>ACQ<1>  | FORCE<br>ACQ<0> | FORCE<br>DISP<1>          | FORCE<br>DISP<0>              | SCREEN<br>COL<2> | SCREEN<br>COL<1> | SCREEN<br>COL<0> |

| BAH | R   | WSS1   | 0                   | 0                | 0               | WSS<3:0><br>ERROR         | WSS<3>                        | WSS<2>           | WSS<1>           | WSS<0>           |

| BBH | R   | WSS2   | 0                   | 0                | 0               | WSS<7:4><br>ERROR         | WSS<7>                        | WSS<6>           | WSS<5>           | WSS<4>           |

| BCH | R   | WSS3   | WSS<13:11><br>ERROR | WSS<13>          | WSS<12>         | WSS<11>                   | WSS<10:8><br>ERROR            | WSS<10>          | WSS<9>           | WSS<8>           |

| BEH | R/W | P3CFGA | Reserved            | Reserved         | Reserved        | Reserved                  | P3CFGA<3>                     | P3CFGA<2>        | P3CFGA<1>        | P3CFGA<0>        |

| BFH | R/W | P3CFGB | Reserved            | Reserved         | Reserved        | Reserved                  | P3CFGB<3>                     | P3CFGB<2>        | P3CFGB<1>        | P3CFGB<0>        |

| СОН | R/W | ТХТО   | X24 POSN            | DISPLAY<br>X24   | AUTO<br>FRAME   | DISABLE<br>HEADER<br>ROLL | DISPLAY<br>STATUS<br>ROW ONLY | DISABLE<br>FRAME | VPS ON           | INV ON           |

Table 2 SFR Map

# TDA935X/6X/8X PS/N2 series

| ADD | R/W | Names  | BIT7                    | BIT6                    | BIT5          | BIT4                        | BIT3               | BIT2              | BIT1              | BITO                       |

|-----|-----|--------|-------------------------|-------------------------|---------------|-----------------------------|--------------------|-------------------|-------------------|----------------------------|

| C1H | R/W | TXT1   | EXT PKT<br>OFF          | 8 BIT                   | ACQ OFF       | X26 OFF                     | FULL<br>FIELD      | FIELD<br>POLARITY | H<br>POLARITY     | V<br>POLARITY              |

| C2H | R/W | TXT2   | ACQ BANK                | REQ<3>                  | REQ<2>        | REQ<1>                      | REQ<0>             | SC<2>             | SC<1>             | SC<0>                      |

| СЗН | W   | ТХТ3   | -                       | -                       | -             | PRD<4>                      | PRD<3>             | PRD<2>            | PRD<1>            | PRD<0>                     |

| C4H | R/W | TXT4   | OSD BANK<br>ENABLE      | QUAD<br>WIDTH<br>ENABLE | EAST/WES<br>T | DISABLE<br>DOUBLE<br>HEIGHT | B MESH<br>ENABLE   | C MESH<br>ENABLE  | TRANS<br>ENABLE   | SHADOW<br>ENABLE           |

| С5Н | R/W | TXT5   | BKGND<br>OUT            | BKGND IN                | CORB OUT      | CORB IN                     | TEXT OUT           | TEXT IN           | PICTURE<br>ON OUT | PICTURE<br>ON IN           |

| С6Н | R/W | TXT6   | BKGND<br>OUT            | BKGND IN                | CORB OUT      | CORB IN                     | TEXT OUT           | TEXT IN           | PICTURE<br>ON OUT | PICTURE<br>ON IN           |

| С7Н | R/W | TXT7   | STATUS<br>ROW TOP       | CURSOR<br>ON            | REVEAL        | BOTTOM/<br>TOP              | DOUBLE<br>HEIGHT   | BOX ON 24         | BOX ON<br>1-23    | BOX ON 0                   |

| C8H | R/W | ТХТ8   | (Reserved)<br>0         | FLICKER<br>STOP ON      | HUNT          | DISABLE<br>SPANISH          | PKT 26<br>RECEIVED | WSS<br>RECEIVED   | WSS ON            | CVBS1/<br>CVBS0            |

| С9Н | R/W | ТХТ9   | CURSOR<br>FREEZE        | CLEAR<br>MEMORY         | A0            | R<4>                        | R<3>               | R<2>              | R<1>              | R<0>                       |

| САН | R/W | TXT10  | 0                       | 0                       | C<5>          | C<4>                        | C<3>               | C<2>              | C<1>              | C<0>                       |

| СВН | R/W | TXT11  | D<7>                    | D<6>                    | D<5>          | D<4>                        | D<3>               | D<2>              | D<1>              | D<0>                       |

| ССН | R   | TXT12  | 525/ <u>625</u><br>SYNC | ROM<br>VER<4>           | ROM<br>VER<3> | ROM<br>VER<2>               | ROM<br>VER<1>      | ROM<br>VER<0>     | 1                 | VIDEO<br>SIGNAL<br>QUALITY |

| CDH | R/W | TXT14  | 0                       | 0                       | 0             | DISPLAY<br>BANK             | PAGE<3>            | PAGE<2>           | PAGE<1>           | PAGE<0>                    |

| СЕН | R/W | TXT15  | 0                       | 0                       | 0             | MICRO<br>BANK               | BLOCK<3>           | BLOCK<2>          | BLOCK<1>          | BLOCK<0>                   |

| D0H | R/W | PSW    | С                       | AC                      | F0            | RS1                         | RS0                | OV                | -                 | Р                          |

| D2H | R/W | TDACL  | TD<7>                   | TD<6>                   | TD<5>         | TD<4>                       | TD<3>              | TD<2>             | TD<1>             | TD<0>                      |

| D3H | R/W | ТДАСН  | TPWE                    | 1                       | TD<13>        | TD<12>                      | TD<11>             | TD<10>            | TD<9>             | TD<8>                      |

| D5H | R/W | PWM0   | PW0E                    | 1                       | PW0V<5>       | PW0V<4>                     | PW0V<3>            | PW0V<2>           | PW0V<1>           | PW0V<0>                    |

| D6H | R/W | PWM1   | PW1E                    | 1                       | PW1V<5>       | PW1V<4>                     | PW1V<3>            | PW1V<2>           | PW1V<1>           | PW1V<0>                    |

| D7H | R   | CCDAT1 | CCD1<7>                 | CCD1<6>                 | CCD1<5>       | CCD1<4>                     | CCD1<3>            | CCD1<2>           | CCD1<1>           | CCD1<0>                    |

| D8H | R/W | S1CON  | CR<2>                   | ENSI                    | STA           | STO                         | SI                 | AA                | CR<1>             | CR<0>                      |

| D9H | R   | S1STA  | STAT<4>                 | STAT<3>                 | STAT<2>       | STAT<1>                     | STAT<0>            | 0                 | 0                 | 0                          |

| DAH | R/W | S1DAT  | DAT<7>                  | DAT<6>                  | DAT<5>        | DAT<4>                      | DAT<3>             | DAT<2>            | DAT<1>            | DAT<0>                     |

| DBH | R/W | S1ADR  | ADR<6>                  | ADR<5>                  | ADR<4>        | ADR<3>                      | ADR<2>             | ADR<1>            | ADR<0>            | GC                         |

| DCH | R/W | PWM3   | PW3E                    | 1                       | PW3V<5>       | PW3V<4>                     | PW3V<3>            | PW3V<2>           | PW3V<1>           | PW3V<0>                    |

| E0H | R/W | ACC    | ACC<7>                  | ACC<6>                  | ACC<5>        | ACC<4>                      | ACC<3>             | ACC<2>            | ACC<1>            | ACC<0>                     |

| E4H | R/W | PWM2   | PW2E                    | 1                       | PW2V<5>       | PW2V<4>                     | PW2V<3>            | PW2V<2>           | PW2V<1>           | PW2V<0>                    |

Table 2 SFR Map

# TDA935X/6X/8X PS/N2 series

| ADD | R/W | Names  | BIT7            | BIT6             | BIT5           | BIT4     | BIT3     | BIT2     | BIT1     | BITO     |

|-----|-----|--------|-----------------|------------------|----------------|----------|----------|----------|----------|----------|

| E7H | R   | CCDAT2 | CCD2<7>         | CCD2<6>          | CCD2<5>        | CCD2<4>  | CCD2<3>  | CCD2<2>  | CCD2<1>  | CCD2<0>  |

| E8H | R/W | SAD    | VHI             | CH<1>            | CH<0>          | ST       | SAD<7>   | SAD<6>   | SAD<5>   | SAD<4>   |

| F0H | R/W | В      | B<7>            | B<6>             | B<5>           | B<4>     | B<3>     | B<2>     | B<1>     | B<0>     |

| F8H | R/W | TXT13  | VPS<br>RECEIVED | PAGE<br>CLEARING | 525<br>DISPLAY | 525 TEXT | 625 TEXT | PKT 8/30 | FASTEXT  | 0        |

| FAH | R/W | XRAMP  | XRAMP<7>        | XRAMP<6>         | XRAMP<5>       | XRAMP<4> | XRAMP<3> | XRAMP<2> | XRAMP<1> | XRAMP<0> |

| FBH | R/W | ROMBK  | STANDBY         | IIC_LUT<1>       | IIC_LUT<0>     | 0        | 0        | 0        | ROMBK<1> | ROMBK<0> |

| FDH | R   | TEST   | TEST<7>         | TEST<6>          | TEST<5>        | TEST<4>  | TEST<3>  | TEST<2>  | TEST<1>  | TEST<0>  |

| FEH | W   | WDTKEY | WKEY<7>         | WKEY<6>          | WKEY<5>        | WKEY<4>  | WKEY<3>  | WKEY<2>  | WKEY<1>  | WKEY<0>  |

| FFH | R/W | WDT    | WDV<7>          | WDV<6>           | WDV<5>         | WDV<4>   | WDV<3>   | WDV<2>   | WDV<1>   | WDV<0>   |

Table 2 SFR Map

A description of each of the SFR bits is shown in Table 3, The SFRs are in alphabetical order.

| Names     | ADD     | BIT7                                             | BIT6               | BIT5               | BIT4             | BIT3    | BIT2    | BIT1    | BITO    | RESET |  |  |

|-----------|---------|--------------------------------------------------|--------------------|--------------------|------------------|---------|---------|---------|---------|-------|--|--|

| ACC       | E0H     | ACC<7>                                           | ACC<6>             | ACC<5>             | ACC<4>           | ACC<3>  | ACC<2>  | ACC<1>  | ACC<0>  | 00H   |  |  |

| ACC<7:0>  | Accumu  | ilator value.                                    |                    |                    |                  |         |         |         |         |       |  |  |

| В         | F0H     | B<7>                                             | B<6>               | B<5>               | B<4>             | B<3>    | B<2>    | B<1>    | B<0>    | 00H   |  |  |

| B<7:0>    | B Regis | ter value.                                       |                    |                    |                  |         |         |         |         |       |  |  |

| CCDAT1    | D7H     | CCD1<7>                                          | CCD1<6>            | CCD1<5>            | CCD1<4>          | CCD1<3> | CCD1<2> | CCD1<1> | CCD1<0> | 00H   |  |  |

| CCD1<7:0> | Closed  | Caption first data                               | ı byte.            | •                  |                  |         |         | •       | •       |       |  |  |

| CCDAT2    | E7H     | CCD2<7>                                          | CCD2<6>            | CCD2<5>            | CCD2<4>          | CCD2<3> | CCD2<2> | CCD2<1> | CCD2<0> | 00H   |  |  |

| CCD2<7:0> | Closed  | Caption second d                                 | lata byte.         |                    |                  |         |         |         |         |       |  |  |

| CCLIN     | B7H     | 0                                                | 0                  | 0                  | CS<4>            | CS<3>   | CS<2>   | CS<1>   | CS<0>   | 15H   |  |  |

| CS<4:0>   | Closed  | Closed Caption Slice line using 525 line number. |                    |                    |                  |         |         |         |         |       |  |  |

| DPH       | 83H     | DPH<7>                                           | DPH<6>             | DPH<5>             | DPH<4>           | DPH<3>  | DPH<2>  | DPH<1>  | DPH<0>  | 00H   |  |  |

| DPH<7:0>  | Data Po | inter High byte,                                 | used with DPL to   | o address display  | and auxiliary m  | emory.  |         |         |         | •     |  |  |

| DPL       | 82H     | DPL<7>                                           | DPL<6>             | DPL<5>             | DPL<4>           | DPL<3>  | DPL<2>  | DPL<1>  | DPL<0>  | 00H   |  |  |

| DPL<7:0>  | Data po | inter low byte, u                                | sed with DPH to    | address display    | and auxiliary me | mory.   |         |         |         |       |  |  |

| IE        | A8H     | EA                                               | EBUSY              | ES2                | ECC              | ET1     | EX1     | ET0     | EX0     | 00H   |  |  |

| EA        | Disable | all interrupts (0)                               | , or use individua | al interrupt enabl | e bits (1).      |         |         |         |         | •     |  |  |

| EBUSY     | Enable  | Enable BUSY Interrupt.                           |                    |                    |                  |         |         |         |         |       |  |  |

| ES2       | Enable  | Enable I <sup>2</sup> C Interrupt.               |                    |                    |                  |         |         |         |         |       |  |  |

| ECC       | Enable  | Closed Caption I                                 | nterrupt.          |                    |                  |         |         |         |         |       |  |  |

# TDA935X/6X/8X PS/N2 series

| Names   | ADD           | BIT7                                            | BIT6               | BIT5       | BIT4     | BIT3      | BIT2      | BIT1      | BIT0      | RESET |  |  |  |

|---------|---------------|-------------------------------------------------|--------------------|------------|----------|-----------|-----------|-----------|-----------|-------|--|--|--|

| ET1     | Enable        | Fimer 1 Interrup                                | i.                 |            |          |           |           |           |           |       |  |  |  |

| EX1     | Enable l      | External Interrup                               | t 1.               |            |          |           |           |           |           |       |  |  |  |

| ET0     | Enable        | Fimer 0 Interrup                                | i.                 |            |          |           |           |           |           |       |  |  |  |

| EX0     | Enable l      | External Interrup                               | t 0.               |            |          |           |           |           |           |       |  |  |  |

| IEN1    | 84H           | -                                               | -                  | -          | -        | -         | -         | -         | ET2       | 00H   |  |  |  |

| ET2     | Enable        | Fimer 2 Interrup                                | i.                 |            |          |           |           |           |           |       |  |  |  |

| IP      | B8H           | 0                                               | PBUSY              | PES2       | PCC      | PT1       | PX1       | PT0       | PX0       | 00H   |  |  |  |

| PBUSY   | Priority      | EBUSY Interrup                                  | ot.                |            |          |           |           |           |           |       |  |  |  |

| PES2    | Priority      | ES2 Interrupt.                                  |                    |            |          |           |           |           |           |       |  |  |  |

| PCC     | Priority      | ECC Interrupt.                                  |                    |            |          |           |           |           |           |       |  |  |  |

| PT1     | Priority      | Timer 1 Interrup                                | vt.                |            |          |           |           |           |           |       |  |  |  |

| PX1     | Priority      | External Interru                                | pt 1.              |            |          |           |           |           |           |       |  |  |  |

| PT0     | Priority      | riority Timer 0 Interrupt.                      |                    |            |          |           |           |           |           |       |  |  |  |

| PX0     | Priority      | External Interru                                | pt 0.              |            |          |           |           |           |           |       |  |  |  |

| IP1     | 85H           | -                                               | -                  | -          | -        | -         | -         | -         | PT2       | 00H   |  |  |  |

| PT2     | Priority      | Timer 2 Interrup                                | ıt.                |            |          |           |           |           | •         |       |  |  |  |

| PO      | 80H           | Reserved                                        | P0<6>              | P0<5>      | Reserved | Reserved  | Reserved  | Reserved  | Reserved  | FFH   |  |  |  |

| P0<6:5> | Port 0 I/     | O register conne                                | cted to external I | oins.      |          |           |           |           |           |       |  |  |  |

| P1      | 90H           | P1<7>                                           | P1<6>              | Reserved   | Reserved | P1<3>     | P1<2>     | P1<1>     | P1<0>     | FFH   |  |  |  |

| P1<7:6> | Port 1 I/     | O register conne                                | cted to external p | oins.      |          |           |           |           |           |       |  |  |  |

| P1<3:0> | Port 1 I/     | O register conne                                | cted to external I | oins.      |          |           |           |           |           |       |  |  |  |

| P2      | A0H           | Reserved                                        | P2<6>              | P2<5>      | P2<4>    | P2<3>     | P2<2>     | P2<1>     | P2<0>     | FFH   |  |  |  |

| P2<6:0> | Port 2 I/     | O register conne                                | cted to external p | oins.      |          |           |           |           |           |       |  |  |  |

| Р3      | B0H           | Reserved                                        | Reserved           | Reserved   | Reserved | P3<3>     | P3<2>     | P3<1>     | P3<0>     | FFH   |  |  |  |

| P3<3:0> | Port 3 I/     | O register conne                                | cted to external p | oins.      |          |           |           |           |           |       |  |  |  |

| POCFGA  | 96H           | Reserved                                        | P0CFGA<6>          | P0CFGA<5>  | Reserved | Reserved  | Reserved  | Reserved  | Reserved  | FFH   |  |  |  |

| P0CFGB  | 97H           | Reserved                                        | P0CFGB<6>          | P0CFGB<5>  | Reserved | Reserved  | Reserved  | Reserved  | Reserved  | 00H   |  |  |  |

| P0CFG   | B <x>/P0C</x> | FGA < x > = 00                                  | MODE 0 Oper        | n Drain.   |          |           |           |           |           |       |  |  |  |

| P0CFGI  | B <x>/P0C</x> | 0CFGA <x> = 01 MODE 1 Quasi Bi-Directional.</x> |                    |            |          |           |           |           |           |       |  |  |  |

| P0CFG   | B <x>/P0C</x> | FGA < x > = 10                                  | MODE2 High         | Impedance. |          |           |           |           |           |       |  |  |  |

| P0CFG   | B <x>/P0C</x> | FGA <x> = 11</x>                                | MODE3 Push         | Pull.      |          |           |           |           |           |       |  |  |  |

| P1CFGA  | 9EH           | P1CFGA<7>                                       | P1CFGA<6>          | Reserved   | Reserved | P1CFGA<3> | P1CFGA<2> | P1CFGA<1> | P1CFGA<0> | FFH   |  |  |  |

| P1CFGB  | 9FH           | P1CFGB<7>                                       | P1CFGB<6>          | Reserved   | Reserved | P1CFGB<3> | P1CFGB<2> | P1CFGB<1> | P1CFGB<0> | 00H   |  |  |  |

# TDA935X/6X/8X PS/N2 series

| Names   | ADD                                                 | BIT7                                                                                                                                                                         | BIT6               | BIT5                | BIT4               | BIT3      | BIT2      | BIT1      | BIT0      | RESET |

|---------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|--------------------|-----------|-----------|-----------|-----------|-------|

| P1CFC   | Best Best Best Best Best Best Best Best             | 2FGA < x > = 00                                                                                                                                                              | MODE 0 Oper        | n Drain.            |                    |           |           |           |           |       |

| P1CFC   | Best Best Best Best Best Best Best Best             | 2FGA < x > = 01                                                                                                                                                              | MODE 1 Qua         | si Bi-Directional   |                    |           |           |           |           |       |

| P1CFC   | Best Best Best Best Best Best Best Best             | 2FGA < x > = 10                                                                                                                                                              | MODE2 High         | Impedance.          |                    |           |           |           |           |       |

| P1CFC   | Best Best Best Best Best Best Best Best             | 2FGA < x > = 11                                                                                                                                                              | MODE3 Push         | Pull.               |                    |           |           |           |           |       |

| P2CFGA  | A6H                                                 | Reserved                                                                                                                                                                     | P2CFGA<6>          | P2CFGA<5>           | P2CFGA<4>          | P2CFGA<3> | P2CFGA<2> | P2CFGA<1> | P2CFGA<0> | FFH   |

| P2CFGB  | A7H                                                 | Reserved                                                                                                                                                                     | P2CFGB<6>          | P2CFGB<5>           | P2CFGB<4>          | P2CFGB<3> | P2CFGB<2> | P2CFGB<1> | P2CFGB<0> | 00H   |

| P2CFC   | B <x>/P2C</x>                                       | 2FGA < x > = 00                                                                                                                                                              | MODE 0 Oper        | n Drain.            |                    |           |           |           |           |       |

| P2CFC   | B <x>/P2C</x>                                       | 2FGA < x > = 01                                                                                                                                                              | MODE 1 Qua         | si Bi-Directional   |                    |           |           |           |           |       |

| P2CFC   | B <x>/P2C</x>                                       | 2FGA < x > = 10                                                                                                                                                              | MODE2 High         | Impedance.          |                    |           |           |           |           |       |

| P2CFC   | B <x>/P2C</x>                                       | 2FGA <x> = 11</x>                                                                                                                                                            | MODE3 Push         | Pull.               |                    |           |           |           |           |       |

| P3CFGA  | BEH                                                 | Reserved                                                                                                                                                                     | Reserved           | Reserved            | Reserved           | P3CFGA<3> | P3CFGA<2> | P3CFGA<1> | P3CFGA<0> | FFH   |

| P3CFGB  | BFH                                                 | Reserved                                                                                                                                                                     | Reserved           | Reserved            | Reserved           | P3CFGB<3> | P3CFGB<2> | P3CFGB<1> | P3CFGB<0> | 00H   |

| P3CFC   | B <x>/P3C</x>                                       | 2FGA < x > = 00                                                                                                                                                              | MODE 0 Oper        | n Drain.            |                    |           |           | 1         |           | 1     |

| P3CFC   | B <x>/P3C</x>                                       | 2FGA < x > = 01                                                                                                                                                              | MODE 1 Qua         | si Bi-directional.  |                    |           |           |           |           |       |

| P3CFC   | B <x>/P3C</x>                                       | 2FGA < x > = 10                                                                                                                                                              | MODE2 High         | Impedance.          |                    |           |           |           |           |       |

| P3CFC   | B <x>/P3C</x>                                       | 2FGA <x> = 11</x>                                                                                                                                                            | MODE3 Push         | Pull.               |                    |           |           |           |           |       |

| PCON    | 87H                                                 | SMOD                                                                                                                                                                         | ARD                | RFI                 | WLE                | GF1       | GF0       | PD        | IDL       | 00H   |

| SMOD    | UART I                                              | Baud Rate Doubl                                                                                                                                                              | e Control.         |                     |                    |           |           | 1         |           | 1     |

| ARD     | Auxilia                                             | ry RAM Disable                                                                                                                                                               | , All MOVX inst    | ructions access the | he external data 1 | nemory.   |           |           |           |       |

| RFI     | Disable                                             | ALE during inte                                                                                                                                                              | rnal access to re- | luce Radio Frequ    | uency Interference | e.        |           |           |           |       |

| WLE     | Watch I                                             | Dog Timer enable                                                                                                                                                             | 2.                 |                     |                    |           |           |           |           |       |

| GF1     | General                                             | purpose flag.                                                                                                                                                                |                    |                     |                    |           |           |           |           |       |

| GF0     | General                                             | purpose flag.                                                                                                                                                                |                    |                     |                    |           |           |           |           |       |

| PD      | Power-c                                             | lown activation b                                                                                                                                                            | oit.               |                     |                    |           |           |           |           |       |

| IDL     | Idle mo                                             | de activation bit.                                                                                                                                                           |                    |                     |                    |           |           |           |           |       |

| PSW     | D0H                                                 | С                                                                                                                                                                            | AC                 | F0                  | RS<1>              | RS<0>     | OV        | -         | Р         | 00H   |

| С       | Carry B                                             | it.                                                                                                                                                                          |                    |                     |                    |           |           | 1         |           |       |

| AC      | Auxilia                                             | ry Carry bit.                                                                                                                                                                |                    |                     |                    |           |           |           |           |       |

| F0      | Flag 0,                                             | Flag 0, General purpose flag.                                                                                                                                                |                    |                     |                    |           |           |           |           |       |

| RS<1:0> | RS<1:02<br>RS<1:02<br>RS<1:02<br>RS<1:02<br>RS<1:02 | Register Bank selector bits.<br>RS<1:0> = 00, Bank0 (00H - 07H).<br>RS<1:0> = 01, Bank1 (08H - 0FH).<br>RS<1:0> = 10, Bank2 (10H - 17H).<br>RS<1:0> = 11, Bank3 (18H - 1FH). |                    |                     |                    |           |           |           |           |       |

| OV      | Overflo                                             | w flag.                                                                                                                                                                      |                    |                     |                    |           |           |           |           |       |

# TDA935X/6X/8X PS/N2 series

| Names         | ADD                        | BIT7                                                                                      | BIT6                                     | BIT5       | BIT4    | BIT3    | BIT2    | BIT1     | BITO     | RESET |

|---------------|----------------------------|-------------------------------------------------------------------------------------------|------------------------------------------|------------|---------|---------|---------|----------|----------|-------|

| Р             | Parity bi                  | t.                                                                                        |                                          |            |         |         |         |          |          |       |

| PWM0          | D5H                        | PW0E                                                                                      | 1                                        | PW0V<5>    | PW0V<4> | PW0V<3> | PW0V<2> | PW0V<1>  | PW0V<0>  | 40H   |

| PW0E          |                            | ole Pulse Width M<br>le Pulse Width M                                                     |                                          |            |         |         |         |          |          |       |

| PW0V<5:0>     | Pulse W                    | idth Modulator                                                                            | high time.                               |            |         |         |         |          |          |       |

| PWM1          | D6H                        | PW1E                                                                                      | 1                                        | PW1V<5>    | PW1V<4> | PW1V<3> | PW1V<2> | PW1V<1>  | PW1V<0>  | 40H   |

| PW1E          |                            | ble Pulse Width<br>ble Pulse Width I                                                      |                                          |            | •       |         |         |          |          | ·     |

| PW1V<5:0>     | Pulse W                    | idth Modulator                                                                            | high time.                               |            |         |         |         |          |          |       |

| PWM2          | E4H                        | PW2E                                                                                      | 1                                        | PW2V<5>    | PW2V<4> | PW2V<3> | PW2V<2> | PW2V<1>  | PW2V<0>  | 40H   |

| PW2E          |                            | ble Pulse Width<br>ble Pulse Width I                                                      |                                          |            | •       |         |         |          |          | ·     |

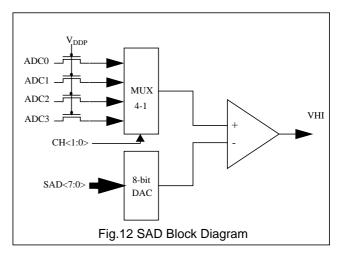

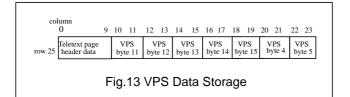

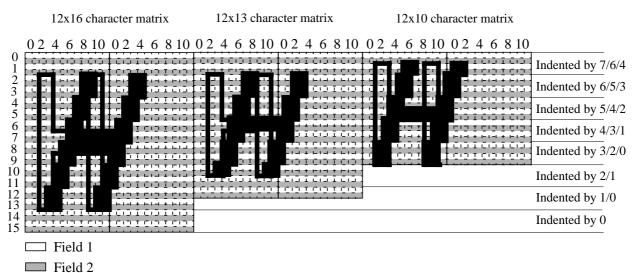

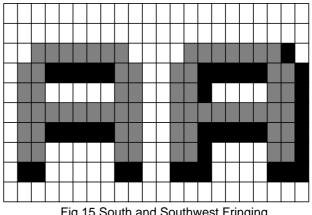

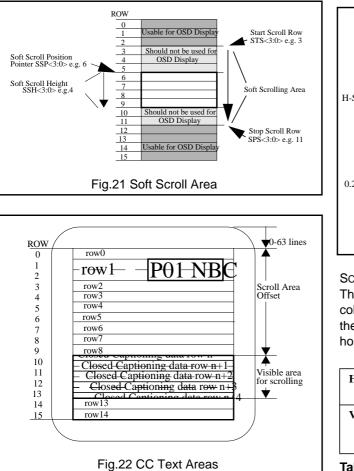

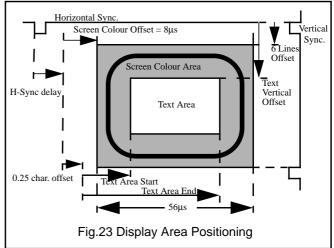

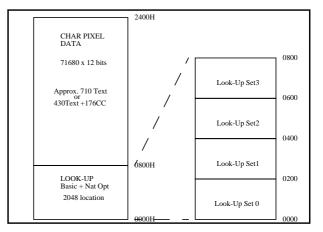

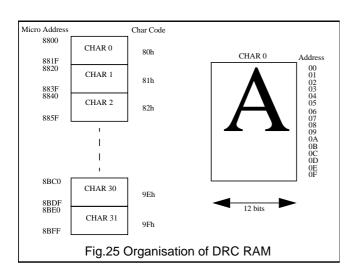

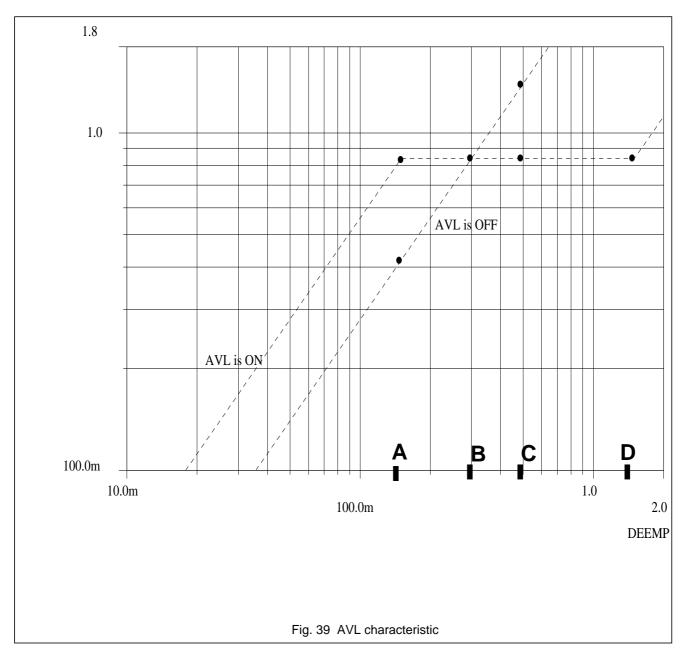

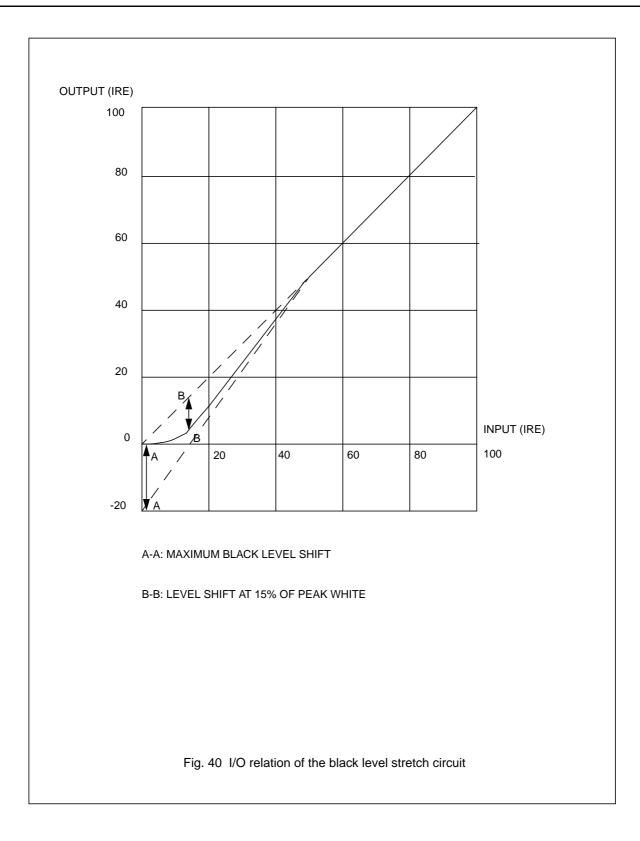

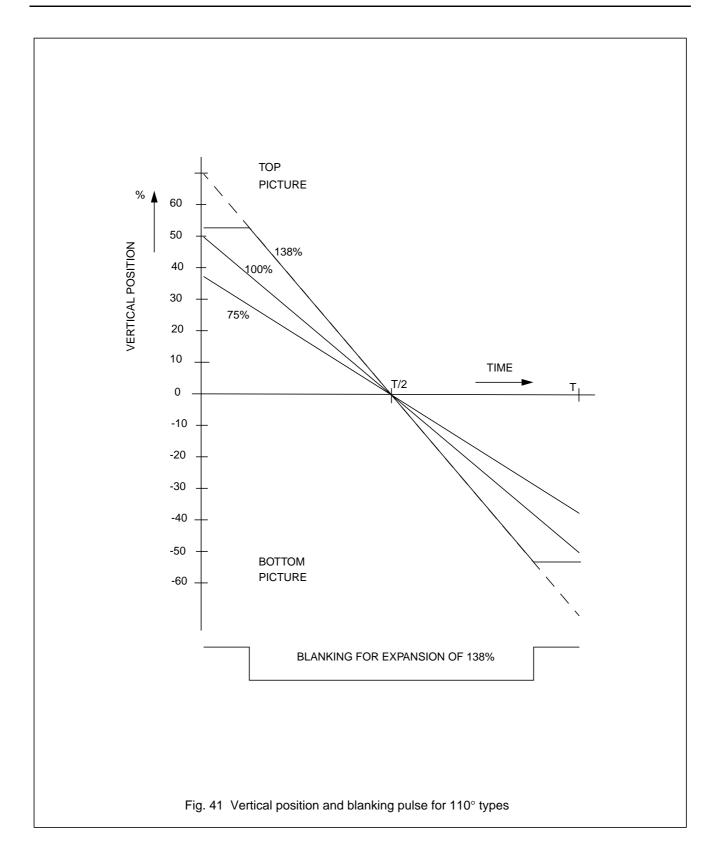

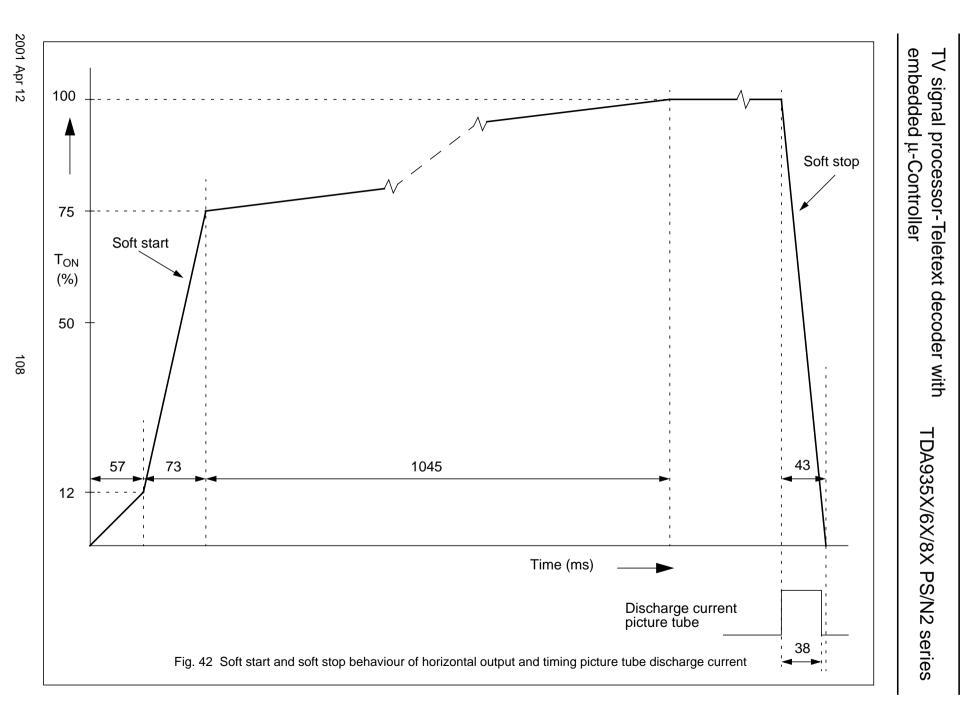

| PW2V<5:0>     | Pulse W                    | idth Modulator                                                                            | high time.                               |            |         |         |         |          |          |       |