# ST6365, ST6375, ST6385 ST6367, ST6377, ST6387

**DATA SHEET**

### USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED.

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics.

As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## **ST6365 DATASHEET INDEX**

| ST6365, ST6375, ST6385                       | Pages    |

|----------------------------------------------|----------|

| ST6367, ST6377, ST6387                       | 1        |

| GENERAL DESCRIPTION                          | 2        |

| PIN DESCRIPTION                              | 4        |

| ST638x CORE                                  | 6        |

| MEMORY SPACES                                | 9        |

| INTERRUPT                                    | 16       |

| RESET                                        | 20       |

| WAIT & STOP MODES                            | 22       |

| ON-CHIP CLOCK OSCILLATOR                     | 23       |

| INPUT/OUTPUT PORTS                           | 24       |

| TIMERS                                       | 27       |

| HARDWARE ACTIVATED DIGITAL WATCHDOG FUNCTION | 30       |

| SERIAL PERIPHERAL INTERFACE                  | 31       |

| 14-BIT VOLTAGE SYNTHESIS TUNING PERIPHERAL   | 40       |

| 6-BIT PWM D/A CONVERTERS                     | 41       |

| AFC A/D COMPARATOR                           | 41       |

| DEDICATED LATCHES                            | 42       |

| ON-SCREEN DISPLAY (OSD)                      | 43       |

| SOFTWARE DESCRIPTION                         | 52       |

| ABSOLUTE MAXIMUM RATINGS                     | 57       |

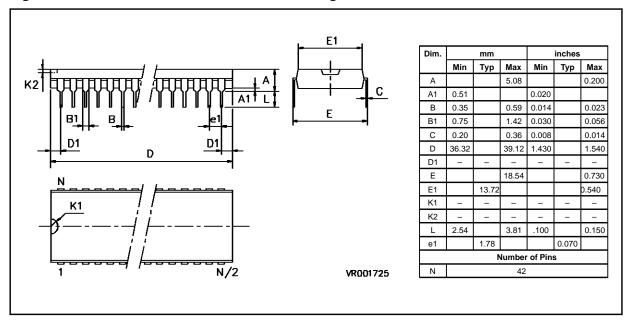

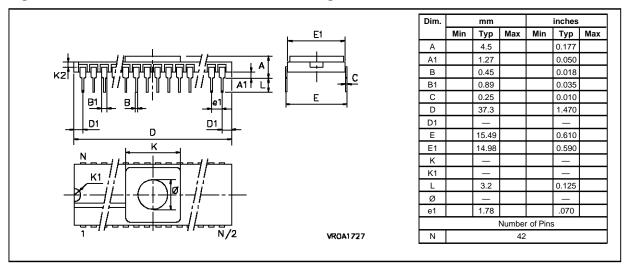

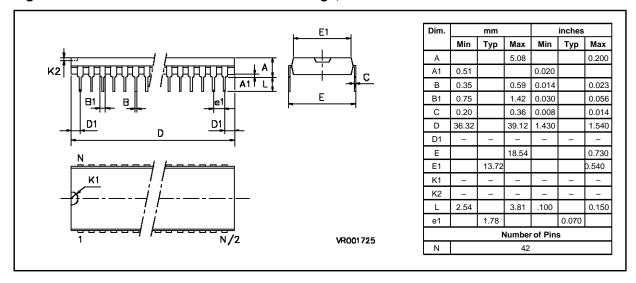

| PACKAGE MECHANICAL DATA                      | 61       |

| ORDERING INFORMATION TABLE                   | 63       |

| ST63E85, T85                                 |          |

| ST63E87, T87                                 | 65       |

| GENERAL DESCRIPTION                          | 66       |

| PIN DESCRIPTION                              | 68       |

| MEMORY SPACE                                 | 70       |

| EPROM/OTP DESCRIPTION                        | 70<br>71 |

| ABSOLUTE MAXIMUM RATINGS                     | 71<br>72 |

| PACKAGE MECHANICAL DATA                      | 72<br>76 |

| ODDEDING INFORMATION                         | 70       |

## ST6365, ST6375, ST6385 ST6367, ST6377, ST6387

# 8-BIT HCMOS MCUs WITH ON-SCREEN DISPLAY FOR TV TUNING

PRELIMINARY DATA

- 4.5 to 6V supply operating range

- 8MHz Maximum Clock Frequency

- User Program ROM: up to 20140 bytes

Reserved Test ROM: up to 340 bytes

Data ROM: user selectable size

Data RAM: 256 bytes

Data EEPROM: 384 bytes

- 42-Pin Shrink Dual in Line Plastic Package

- Up to 22 software programmable general purpose Inputs/Outputs, including 2 direct LED driving Outputs

- Two Timers each including an 8-bit counter with a 7-bit programmable prescaler

- Digital Watchdog Function

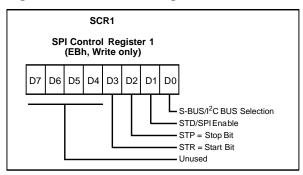

- Serial Peripheral Interface (SPI) supporting S-BUS/I<sup>2</sup>C BUS and standard serial protocols

- SPI for external frequency synthesis tuning

- 14 bit counter for voltage synthesis tuning

- Up to Six 6-Bit PWM D/A Converters

- AFC A/D converter with 0.5V resolution

- Five interrupt vectors (IRIN/NMI, Timer 1 & 2, VSYNC, PWR INT.)

- On-chip clock oscillator

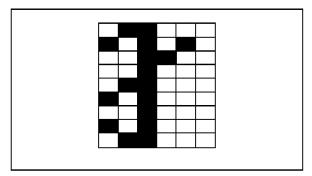

- 5 Lines by 15 Characters On-Screen Display Generator with 128 Characters

- All ROM types are supported by pin-to-pin EPROM, and OTP versions.

- The development tool of the ST636x,7x,8x microcontrollers consists of the ST638x-EMU emulation and development system to be connected via a standard RS232 serial line to an MS-DOS Personal Computer.

#### **DEVICE SUMMARY**

| DEVICE | ROM<br>(Bytes) | D/A Converter |

|--------|----------------|---------------|

| ST6365 | 8K             | 4             |

| ST6367 | 8K             | 6             |

| ST6375 | 14K            | 4             |

| ST6377 | 14K            | 6             |

| ST6385 | 20K            | 4             |

| ST6387 | 20K            | 6             |

October 1993 1/79

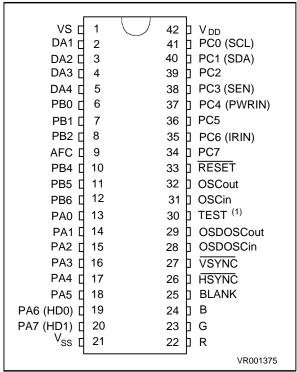

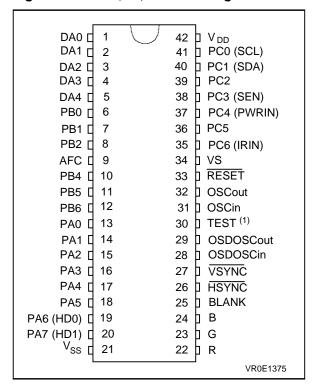

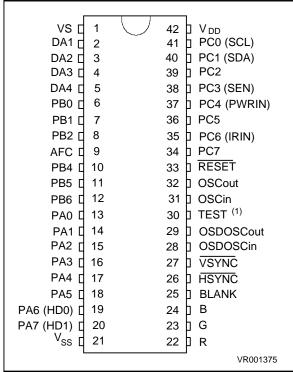

Figure 2. ST6365, 75, 85 Pin Configuration

Note 1. This pin is also the VPP input for EPROM based devices

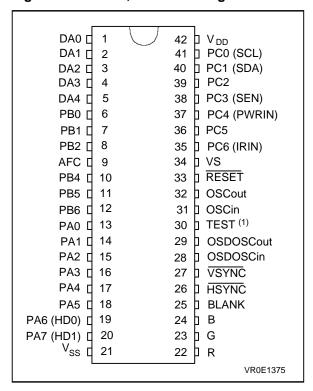

#### Figure 1. ST6367, 77, 87 Pin Configuration

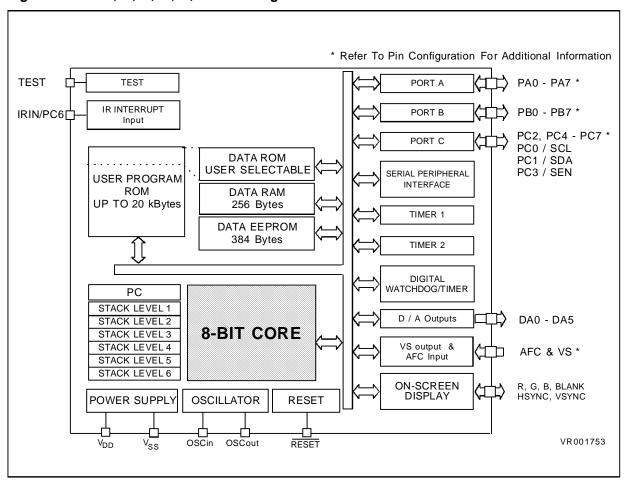

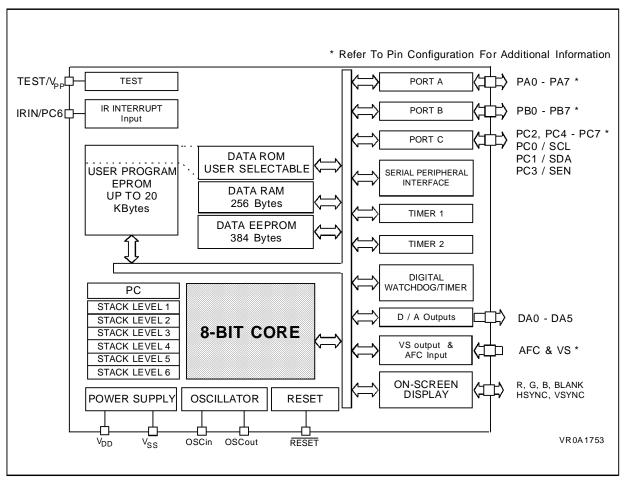

#### GENERAL DESCRIPTION

The ST6365,67,75,77,85,87 microcontrollers are members of the 8-bit HCMOS ST638x family, a series of devices specially oriented to TV applications. Different ROM size and peripheral configurations are available to give the maximum application and cost flexibility. All ST638x members are based on a building block approach: a common core is surrounded by a combination of on-chip peripherals (macrocells) available from a standard library. These peripherals are designed with the same Core technology providing full compatibility and short design time. Many of these macrocells are specially dedicated to TV applications. The macrocells of the ST638x family are: two Timer peripherals each including an 8-bit counter with a 7-bit software pro-

grammable prescaler (Timer), a digital hardware activated watchdog function (DHWD), a 14-bit voltage synthesis tuning peripheral, a Serial Peripheral Interface (SPI), up to six 6-bit PWM D/A converters, an AFC A/D converter with 0.5V resolution, an on-screen display (OSD) with 15 characters per line and 128 characters (in two banks each of 64 characters). In addition the following memory resources are available: program ROM (up to 20K), data RAM (256 bytes), EEPROM (384 bytes). Refer to pin configurations figures and to ST638x device summary (Table 1) for the definition of ST638x family members and a summary of differences among the different types.

Figure 3. ST6365,67,75,77,85,87 Block Diagram

**Table 1. Device Summary**

| DEVICE | ROM<br>(Bytes) | RAM<br>(Bytes) | EEPROM<br>(Bytes) | AFC | vs  | D/A | COLOUR<br>PINS | EMULATING<br>DEVICES |

|--------|----------------|----------------|-------------------|-----|-----|-----|----------------|----------------------|

| ST6365 | 8K             | 256            | 384               | YES | YES | 4   | 3              | ST63P85, ST63E85     |

| ST6367 | 8K             | 256            | 384               | YES | YES | 6   | 3              | ST63P87, ST63E87     |

| ST6375 | 14K            | 256            | 384               | YES | YES | 4   | 3              | ST63P85, ST63E85     |

| ST6377 | 14K            | 256            | 384               | YES | YES | 6   | 3              | ST63P87, ST63E87     |

| ST6385 | 20K            | 256            | 384               | YES | YES | 4   | 3              | ST63P85, ST63E85     |

| ST6387 | 20K            | 256            | 384               | YES | YES | 6   | 3              | ST63P87, ST63E87     |

#### PIN DESCRIPTION

$V_{DD}$  and  $V_{SS}$ . Power is supplied to the MCU using these two pins.  $V_{DD}$  is power and  $V_{SS}$  is the ground connection.

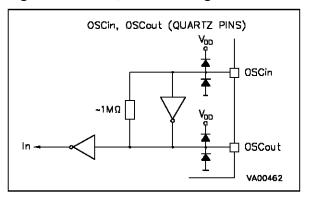

**OSCin, OSCout.** These pins are internally connected to the on-chip oscillator circuit. A quartz crystal or a ceramic resonator can be connected between these two pins in order to allow the correct operation of the MCU with various stability/cost trade-offs. The OSCin pin is the input pin, the OSCout pin is the output pin.

**RESET.** The active low RESET pin is used to start the microcontroller to the beginning of its program. Additionally the quartz crystal oscillator will be disabled when the RESET pin is low to reduce power consumption during reset phase.

**TEST.** The TEST pin must be held at  $V_{SS}$  for normal operation.

**PA0-PA7.** These 8 lines are organized as one I/O port (A). Each line may be configured as either an input with or without pull-up resistor or as an output under software control of the data direction register. Pins PA4 to PA7 are configured as open-drain outputs (12V drive). On PA4-PA7 pins the input pull-up option is not available while PA6 and PA7 have additional current driving capability (25mA, V<sub>OL</sub>:1V). PA0 to PA3 pins are configured as pushpull.

**PB0-PB2**, **PB4-PB6**. These 6 lines are organized as one I/O port (B). Each line may be configured as either an input with or without internal pull-up resistor or as an output under software control of the data direction register.

**PC0-PC7.** These 8 lines are organized as one I/O port (C). Each line may be configured as either an input with or without internal pull-up resistor or as an output under software control of the data direction register. Pins PC0 to PC3 are configured as open-drain (5V drive) in output mode while PC4 to PC7 are open-drain with 12V drive and the input pull-up options does not exist on these four pins.

PC0, PC1 and PC3 lines when in output mode are "ANDed" with the SPI control signals and are all open-drain. PC0 is connected to the SPI clock signal (SCL), PC1 with the SPI data signal (SDA) while PC3 is connected with SPI enable signal (SEN, used in S-BUS protocol). Pin PC4 and PC6 can also be inputs to software programmable edge sensitive latches which can generate interrupts; PC4 can be connected to Power Interrupt while PC6 can be connected to the IRIN/NMI interrupt line

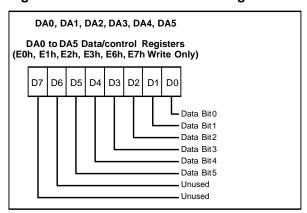

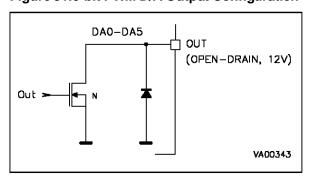

**DA0-DA5.** These pins are the six PWM D/A outputs of the 6-bit on-chip D/A converters. These lines have open-drain outputs with 12V drive. The output repetition rate is 31.25KHz (with 8MHz clock).

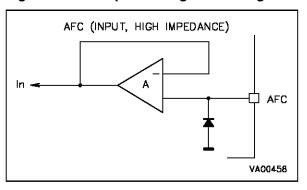

**AFC.** This is the input of the on-chip 10 levels comparator that can be used to implement the AFC function. This pin is an high impedance input able to withstand signals with a peak amplitude up to 12V.

**OSDOSCin, OSDOSCout.** These are the On Screen Display oscillator terminals. An oscillation capacitor and coil network have to be connected to provide the right signal to the OSD.

**HSYNC, VSYNC.** These are the horizontal and vertical synchronization pins. The active polarity of these pins to the OSD macrocell can be selected by the user as ROM mask option. If the device is specified to have negative logic inputs, then these signals are low the OSD oscillator stops. If the device is specified to have positive logic inputs, then when these signals are high the OSD oscillator stops. VSYNC is also connected to the VSYNC interrupt.

**R, G, B, BLANK.** Outputs from the OSD. R, G and B are the color outputs while BLANK is the blanking output. All outputs are push-pull. The active polarity of these pins can be selected by the user as ROM mask option.

**VS.** This is the output pin of the on-chip 14-bit voltage synthesis tuning cell (VS). The tuning signal present at this pin gives an approximate resolution of 40KHz per step over the UHF band. This line is a push-pull output with standard drive.

## **Table 2. Pin Summary**

| Pin Function                      | Description                                                               |

|-----------------------------------|---------------------------------------------------------------------------|

| DA0 to DA5                        | Output, Open-Drain, 12V                                                   |

| AFC                               | Input, High Impedance, 12V                                                |

| VS                                | Output, Push-Pull                                                         |

| R,G,B, BLANK                      | Output, Push-Pull                                                         |

| HSYNC, VSYNC                      | Input, Pull-up, Schmitt Trigger                                           |

| OSDOSCin                          | Input, High Impedance                                                     |

| OSDOSCout                         | Output, Push-Pull                                                         |

| TEST                              | Input, Pull-Down                                                          |

| OSCin                             | Input, Resistive Bias, Schmitt Trigger to Reset Logic Only                |

| OSCout                            | Output, Push-Pull                                                         |

| RESET                             | Input, Pull-up, Schmitt Trigger Input                                     |

| PA0-PA3                           | I/O, Push-Pull, Software Input Pull-up, Schmitt Trigger Input             |

| PA4-PA5                           | I/O, Open-Drain, 12V, No Input Pull-up, Schmitt Trigger Input             |

| PA6-PA7                           | I/O, Open-Drain, 12V, No Input Pull-up, Schmitt Trigger Input, High Drive |

| PB0-PB2                           | I/O, Push-Pull, Software Input Pull-up, Schmitt Trigger Input             |

| PB4-PB6                           | I/O, Push-Pull, Software Input Pull-up, Schmitt Trigger Input             |

| PC0-PC3                           | I/O, Open-Drain, 5V , Software Input Pull-up, Schmitt Trigger Input       |

| PC4-PC7                           | I/O, Open-Drain, 12V, No Input Pull-up, Schmitt Trigger Input             |

| V <sub>DD</sub> , V <sub>SS</sub> | Power Supply Pins                                                         |

#### ST638x CORE

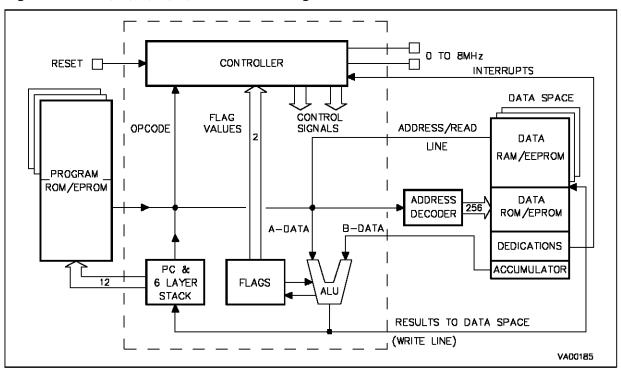

The Core of the ST638x Family is implemented independently from the I/O or memory configuration. Consequently, it can be treated as an independent central processor communicating with I/O and memory via internal addresses, data, and control busses. The in-core communication is arranged as shown in the following block diagram figure; the controller being externally linked to both the reset and the oscillator, while the core is linked to the dedicated on-chip macrocells peripherals via the serial data bus and indirectly for interrupt purposes through the control registers.

#### Registers

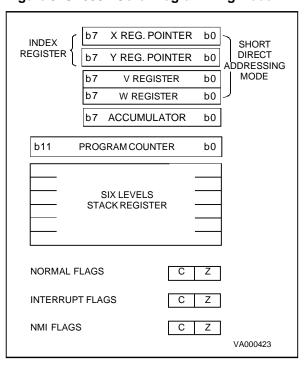

The ST638x Family Core has five registers and three pairs of flags available to the programmer. They are shown in Figure 5 and are explained in the following paragraphs together with the program and data memory page registers.

**Accumulator (A).** The accumulator is an 8-bit general purpose register used in all arithmetic calculations, logical operations, and data manipulations. The accumulator is addressed in the data space as RAM location at the FFh address.

Accordingly, the ST638x instruction set can use the accumulator as any other register of the data space.

Figure 5. ST638x Core Programming Model

Figure 4. ST6365,67,75,77,85,87 Core Block Diagram

#### ST638x CORE (Continued)

Indirect Registers (X, Y). These two indirect registers are used as pointers to the memory locations in the data space. They are used in the register-indirect addressing mode. These registers can be addressed in the data space as RAM locations at the 80h (X) and 81h (Y) addresses. They can also be accessed with the direct, short direct, or bit direct addressing modes. Accordingly, the ST638x instruction set can use the indirect registers as any other register of the data space.

Short Direct Registers (V, W). These two registers are used to save one byte in short direct addressing mode. These registers can be addressed in the data space as RAM locations at the 82h (V) and 83h (W) addresses. They can also be accessed with the direct and bit direct addressing modes. Accordingly, the ST638x instruction set can use the short direct registers as any other register of the data space.

#### Program Counter (PC)

The program counter is a 12-bit register that contains the address of the next ROM location to be processed by the core. This ROM location may be an opcode, an operand, or an address of operand. The 12-bit length allows the direct addressing of 4096 bytes in the program space. Nevertheless, if the program space contains more than 4096 locations, the further program space can be addressed by using the Program ROM Page Register. The PC value is incremented, after it is read for the address of the current instruction, by sending it through the ALU, so giving the address of the next byte in the program. To execute relative jumps the PC and the offset values are shifted through the ALU, where they will be added, and the result is shifted back into the PC. The program counter can be changed in the following ways:

| JP (Jump) instruction              | PC=Jump address     |

|------------------------------------|---------------------|

| CALL instruction                   | PC=Call address     |

| Relative Branch instructions       | PC=PC+offset        |

| Interrupt                          | PC=Interrupt vector |

| Reset                              | PC=Reset vector     |

| <b>RET &amp; RETI instructions</b> | sPC=Pop (stack)     |

| Normal instruction                 | PC=PC+1             |

#### Flags (C, Z)

The ST638x Core includes three pairs of flags that correspond to 3 different modes: normal mode, interrupt mode and Non-Maskable-Interrupt-Mode. Each pair consists of a CARRY flag and a ZERO flag. One pair (CN, ZN) is used during normal operation, one pair is used during the interrupt mode (CI,ZI) and one is used during the not-maskable interrupt mode (CNMI, ZNMI).

The ST638x Core uses the pair of flags that corresponds to the actual mode: as soon as an interrupt (resp. a Non-Maskable-Interrupt) is generated, the ST638x Core uses the interrupt flags (resp. the NMI flags) instead of the normal flags. When the RETI instruction is executed, the normal flags (resp. the interrupt flags) are restored if the MCU was in the normal mode (resp. in the interrupt mode) before the interrupt. Should be observed that each flag set can only be addressed in its own routine (Not-maskable interrupt, normal interrupt or main routine). The interrupt flags are not cleared during the context switching and so, they remain in the state they were at the exit of the last routine switching.

The Carry flag is set when a carry or a borrow occurs during arithmetic operations, otherwise it is cleared. The Carry flag is also set to the value of the bit tested in a bit test instruction, and participates in the rotate left instruction.

The Zero flag is set if the result of the last arithmetic or logical operation was equal to zero, otherwise it is cleared.

The switching between these three sets is automatically performed when an NMI, an interrupt and a RETI instructions occur. As the NMI mode is automatically selected after the reset of the MCU, the ST638x Core uses at first the NMI flags.

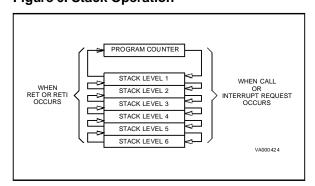

Figure 6. Stack Operation

#### ST638x CORE (Continued)

#### Stack

The ST638x Core includes true LIFO hardware stack that eliminates the need for a stack pointer. The stack consists of six separate 12-bit RAM locations that do not belong to the data space RAM area. When a subroutine call (or interrupt request) occurs, the contents of each level is shifted into the next level while the content of the PC is shifted into the first level (the value of the sixth level will be lost). When subroutine or interrupt return occurs (RET or RETI instructions), the first level register is shifted back into the PC andthe value of each level is shifted back into the previous level. These two operating modes are described in Figure 6. Since the accumulator, as all other data space registers, is not stored in this stack the handling of this registers shall be performed inside the subroutine. The stack pointer will remain in its deepest position, if more than 6 calls or interrupts are executed, so that the last return address will be lost. It will also remain in its highest position if the stack is empty and a RET or RETI is executed. In this case the next instruction will be executed.

#### **Memory Registers**

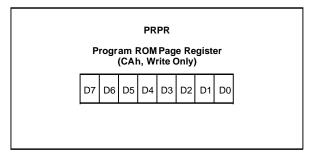

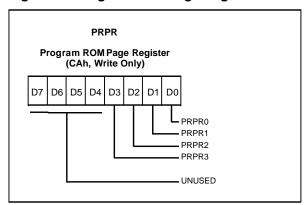

The PRPR can be addressed like a RAM location in the Data Space at the CAh address; nevertheless it is a write-only register that can not be accessed with single-bit operations. This register is used to select the 2-Kbyte ROM bank of the Program Space that will be addressed. The number of the page has to be loaded in the PRPR. The PRPR is not cleared during the MCU initialization and should therefore be defined before jumping out of the static page. Refer to the Program Space description for additional information concerning the use of this register. The PRPR is not modified when an interrupt or a subroutine occurs.

Figure 7. Program ROM Page Register

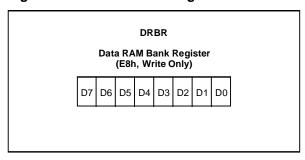

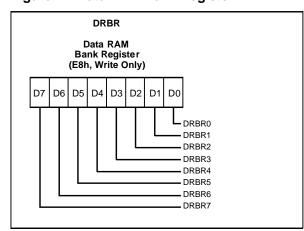

The DRBR can be addressed like a RAM location in the Data Space at the E8h address, nevertheless it is write-only register that can not be accessed with single-bit operations. This register is used to select the desired 64-byte RAM/EEPROM bank of the Data Space. The number of the bank has to be loaded in the DRBR and the instruction has to point to the selected location as it was in the 0 bank (from 00h address to 3Fh address). This register is undefined after Reset. Refer to the Data Space description for additional information. The DRBR register is not modified when a interrupt or a subroutine occurs.

Figure 8. Data RAM Bank Register

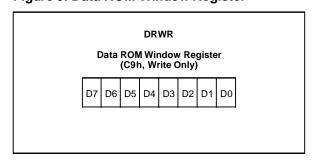

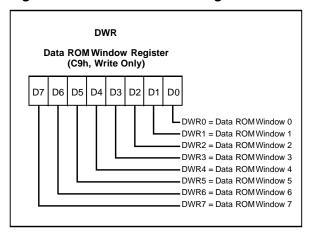

The DRWR register can be addressed like a RAM location in the Data Space at the C9h address, nevertheless it is write-only register that can not be accessed with single-bit operations. This register is used to move up and down the 64-byte read-only data window (from the 40h address to 7Fh address of the Data Space) along the ROM of the MCU by step of 64 bytes. The effective address of the byte to be read as a data in the ROM is obtained by the concatenation of the 6 less significant bits of the address given in the instruction (as less significant bits) and the content of the DRWR (as most significant bits). Refer to the Data Space description for additional information.

Figure 9. Data ROM Window Register

#### **MEMORY SPACES**

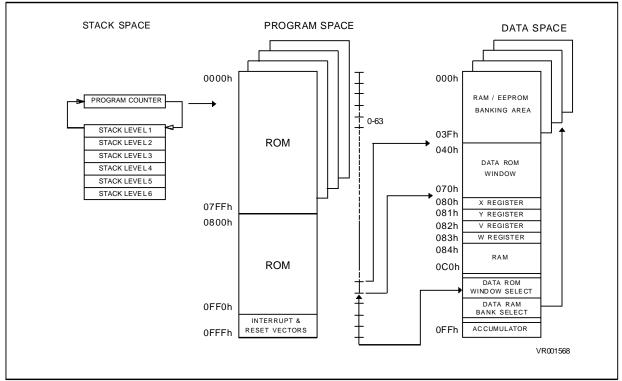

The MCUs operate in three different memory spaces: Stack Space, Program Space, and Data Space. (Figure 10 refers to the ST638x which has a total of 20K bytes of ROM).

#### Stack Space

The stack space consists of six 12 bit registers that are used for stacking subroutine and interrupt return addresses plus the current program counter register.

#### **Program Space**

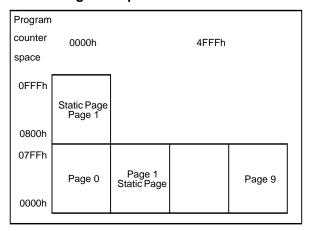

The program space is physically implemented in the ROM and includes all the instructions that are to be executed, as well as the data required for the immediate addressing mode instructions, the reserved test area and user vectors. It is addressed thanks to the 12-bit Program Counter register (PC register) and so, the ST638x Core can directly address up to 4K bytes of Program Space. Nevertheless, the Program Space can be extended by the addition of 2-Kbyte ROM banks as it is shown in Figure 12 in which a 20K bytes memory is described. These banks are addressed by pointing to the 000h-7FFh locations of the Program Space thanks to the Program Counter, and by writing the appropriate code in the Program ROM Page Register (PRPR) located at the CAh address of the Data Space. Because interrupts and common subroutines should be available all the time only the lower 2K byte of the 4K program space are bank

switched while the upper 2K byte can be seen as static space. Table 3 gives the different codes that allows the selection of the corresponding banks. Note that, from the memory point of view, the Page 1 and the Static Page represent the same physical memory: it is only a different way of addressing the same location. On the ST6385 and ST6387, a total of 20480 bytes of ROM have been implemented; 20140 are available as user ROM while 340 are reserved for testing.

Figure 11. ST638x 20K Bytes Program Space Addressing Description

Figure 10. ST638x Memory Addressing Description Diagram

Figure 12. Program ROM Page Register

D7-D5. These bits are not used.

**PRPR4-PRPR0.** These are the program ROM banking bits and the value loaded selects the corresponding page to be addressed in the lower part of 4K program address space as specified in Table 3. This register is undefined on reset.

**Note.** The number of bits implemented depends on the size of the ROM of the device. Only the lower part of address space has been bank-switched because interrupt vectors and common subroutines should be available all the time. The reason of this structure is due to the fact that it is not possible to jump from a dynamic page to another, unless jumping back to the static page, changing contents of PRPR, and, than, jumping to a different dynamic page.

Care is required when handling the PRPR as it is write only. For this reason, it is not allowed to change the PRPR contents while executing interrupts drivers, as the driver cannot save and than restore its previous content. Anyway, this operation may be necessary if the sum of common routines and interrupt drivers will take more than 2K bytes; in this case could be necessary to divide the

interrupt driver in a (minor) part in the static page (start and end), and in the second (major) part in one dynamic page. If it is impossible to avoid the writing of this register in interrupts drivers, an image of this register must be saved in a RAM location, and each time the program writes the PRPR it writes also the image register. The image register must be written first, so if an interrupt occurs between the two instructions the PRPR is not affected.

Table 3. ST636x, 7x, 8x Program ROM Page Register Coding

| PRPR3 | PRPR2 | PRPR1 | PRPR0 | PC11 | Memory<br>Page             |

|-------|-------|-------|-------|------|----------------------------|

| Х     | Х     | Х     | Х     | 1    | Static<br>Page<br>(Page 1) |

| 0     | 0     | 0     | 0     | 0    | Page 0                     |

| 0     | 0     | 0     | 1     | 0    | Page 1<br>(Static<br>Page) |

| 0     | 0     | 1     | 0     | 0    | Page 2                     |

| 0     | 0     | 1     | 1     | 0    | Page 3                     |

| 0     | 1     | 0     | 0     | 0    | Page 4                     |

| 0     | 1     | 0     | 1     | 0    | Page 5                     |

| 0     | 1     | 1     | 0     | 0    | Page 6                     |

| 0     | 1     | 1     | 1     | 0    | Page 7                     |

| 1     | 0     | 0     | 0     | 0    | Page 8                     |

| 1     | 0     | 0     | 1     | 0    | Page 9                     |

## Table 4. ST638x Program ROM Map (up to 20K Bytes)

| ROM Page           | Device Address                                                                         | Description                                                          |

|--------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| PAGE 0             | 0000h-007Fh<br>0080h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 1<br>"STATIC" | 0800h-0F9Fh<br>0FA0h-0FEFh<br>0FF0h-0FF7h<br>0FF8h-0FFBh<br>0FFCh-0FFDh<br>0FFEh-0FFFh | User ROM Reserved Interrupt Vectors Reserved NMI Vector Reset Vector |

| PAGE 2             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 3             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM (End of 8k ST6365, 67)                          |

| PAGE 4             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 5             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 6             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM (End of 14k ST6375, 77)                         |

| PAGE 7             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 8             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM                                                 |

| PAGE 9             | 0000h-000Fh<br>0010h-07FFh                                                             | Reserved<br>User ROM (End of 20k ST6385, 87)                         |

#### **Data Space**

The instruction set of the ST638x Core operates on a specific space, named Data Space that contains all the data necessary for the processing of the program. The Data

Figure 13. ST638x Data Space

| b7 b0                            | 1 000h |

|----------------------------------|--------|

| DATA RAM/EEPROM/OSD<br>BANK AREA |        |

|                                  | 03Fh   |

|                                  | 040h   |

| DATA ROM                         |        |

| WINDOW AREA                      |        |

|                                  | 07Fh   |

| X REGISTER                       | 080h   |

| Y REGISTER                       | 081h   |

| V REGISTER                       | 082h   |

| W REGISTER                       | 083h   |

|                                  | 084h   |

| DATA RAM                         |        |

|                                  | 0BFh   |

| PORT A DATA REGISTER             | 0C0h   |

| PORT B DATA REGISTER             | 0C1h   |

| PORT C DATA REGISTER             | 0C2h   |

| RESERVED                         | 0C3h   |

| PORT A DIRECTION REGISTER        | 0C4h   |

| PORT B DIRECTION REGISTER        | 0C5h   |

| PORT C DIRECTION REGISTER        | 0C6h   |

| RESERVED                         | 0C7h   |

| INTERR UPT OPTION REGISTER       | 0C8h   |

| DATA ROM WINDOW REGISTER         | 0C9h   |

| PROGRAM ROM PAGE REGISTER        | 0CAh   |

| RESERVED                         | 0CBh   |

| SPI DATA REGISTER                | 0CCh   |

|                                  | 0CDh   |

| RESERVED                         |        |

|                                  | 0D1h   |

| TIMER 1 PRESCALER REGISTER       | 0D2h   |

| TIMER 1 COUNTER REGISTER         | 0D3h   |

| TIMER 1 STATUS/CONTROL REG.      | 0D4h   |

|                                  | 0D5h   |

| RESERVED                         |        |

|                                  | 0D7h   |

| WATCHDOG REGISTER                | 0D8h   |

Space allows the addressing of RAM (256 bytes for the ST638x family), EEPROM (384 bytes), ST638x Core/peripheral registers, and read-only data such as constants and the look-up tables.

Figure 14. ST638x Data Space (Continued)

| b7 b0                            |      |

|----------------------------------|------|

| RESERVED                         | 0D9h |

| TIMER 2 PRESCALER REGISTER       | 0DAh |

| TIMER 2 COUNTER REGISTER         | 0DBh |

| TIMER 2 STATUS CONTROL REG.      | 0DCh |

|                                  | 0DDh |

| RESERVED                         |      |

|                                  | 0DFh |

| DA0 DATA/CONTROL REGISTER        | 0E0h |

| DA1 DATA/CONTROL REGISTER        | 0E1h |

| DA2 DATA/CONTROL REGISTER        | 0E2h |

| DA3 DATA/CONTROL REGISTER        | 0E3h |

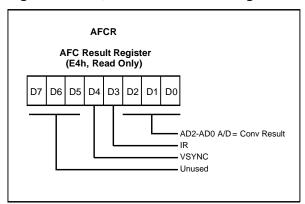

| AFC, IR & OSD RESULT REGISTER    | 0E4h |

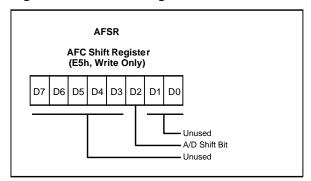

| OUTPUTS CONTROL REGISTER         | 0E5h |

| DA4 DATA/CONTROL REGISTER        | 0E6h |

| DA5 DATA/CONTROL REGISTER        | 0E7h |

| DATA RAM BANK REGISTER           | 0E8h |

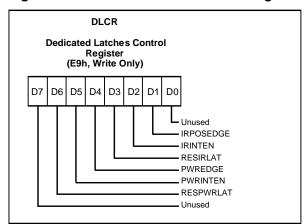

| DEDIC. LATCHES CONTROL REG.      | 0E9h |

| EEPROM CONTROL REGISTER          | 0EAh |

| SPI CONTROL REGISTER 1           | 0EBh |

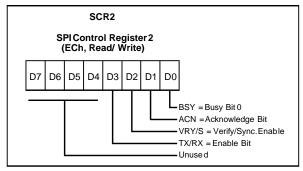

| SPI CONTROL REGISTER 2           | 0ECh |

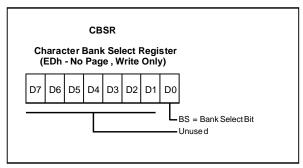

| OSD CHARAC. BANK SELECT REG.     | 0EDh |

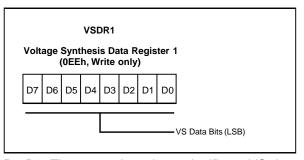

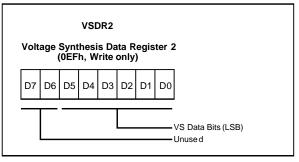

| VS DATA REGISTER 1               | 0EEh |

| VS DATA REGISTER 2               | 0EFh |

| VO BATATREOIOTER 2               | 0F0h |

| RESERVED                         | 0. 0 |

|                                  | 0FEh |

| ACCUMULATOR                      | 0FFh |

|                                  | •    |

| OSD CONTROL REGISTERS<br>LOCATED |      |

| IN PAGE 6 OF BANKED DATA RAM     |      |

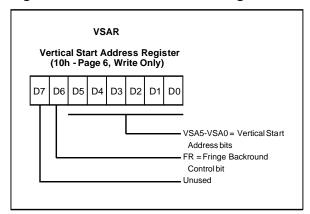

| VERTICAL START ADDRESS REG.      | 010h |

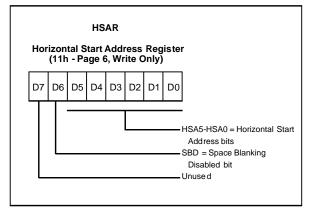

| HORIZONTAL START ADDRESS REG.    | 011h |

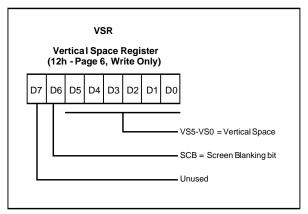

| VERTICAL SPACE REGISTER          | 012h |

| HORIZONTAL SPACE REGISTER        | 013h |

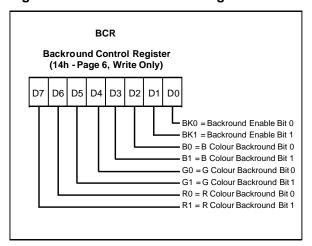

| BACKGROUND COLOUR REGISTER       | 014h |

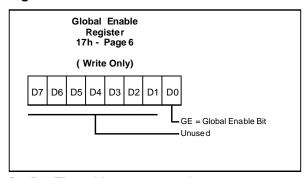

| GLOBAL ENABLE REGISTER           | 017h |

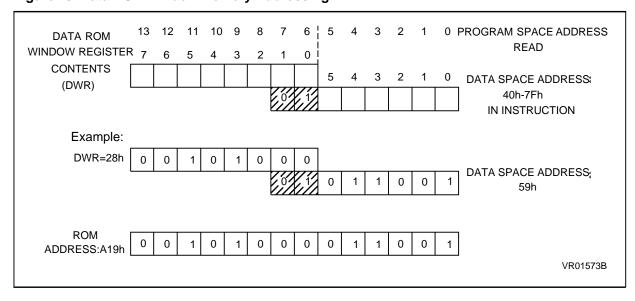

**Data ROM Addressing.** All the read-only data are physically implemented in the ROM in which the Program Space is also implemented. The ROM therefore contains the program to be executed and also the constants and the look-up tables needed for the program. The locations of Data Space in which the different constants and look-up tables are addressed by the ST638x Core can be considered as being a 64-byte window through which it is possible to access to the read-only data stored in the ROM. This window is located from the 40h address to the 7Fh address in the Data space and allows the direct reading of the bytes from the 000h address to the 03Fh address in the ROM. All the bytes of the ROM can be used to store either instructions or read-only data. Indeed, the window can be moved by step of 64 bytes along the ROM in writing the appropriate code in the Write-only Data ROM Window register (DRWR, location C9h). The effective address of the byte to be read as a data in the ROM is obtained by the concatenation of the 6 less significant bits of the address in the Data Space (as less significant bits) and the content of the DRWR (as most significant bits). So when addressing location 40h of data space, and 0 is loaded in the DRWR, the physical addressed location in ROM is 00h.

**Note.** The data ROM window cannot address windows above the 16k byte range.

Figure 15. Data ROM Window Register

**DWR7-DWR0.** These are the Data Rom Window bits that correspond to the upper bits of data ROM program space. This register is undefined after reset.

**Note.** Care is required when handling the DRWR as it is write only. For this reason, it is not allowed to change the DRWR contents while executing interrupts drivers, as the driver cannot save and than restore its previous content. If it is impossible to avoid the writing of this register in interrupts drivers, an image of this register must be saved in a RAM location, and each time the program writes the DRWR it writes also the image register. The image register must be written first, so if an interrupt occurs between the two instructions the DRWR register is not affected.

Figure 16. Data ROM Window Memory Addressing

#### Data RAM/EEPROM/OSD RAM Addressing

In all members of the ST638x family 64 bytes of data RAM are directly addressable in the data space from 80h to BFh addresses. The additional 192 bytes of RAM, the 384 bytes of EEPROM, and the OSD RAM can be addressed using the banks of 64 bytes located between addresses 00h and 3Fh. The selection of the bank is done by programming the Data RAM Bank Register (DRBR) located at the E8h address of the Data Space. In this way each bank of RAM, EEPROM or OSD RAM can select 64 bytes at a time. No more than one bank should be set at a time.

Figure 17. Data RAM Bank Register

**DRBR7,DRBR1,DRBR0.** These bits select the EEPROM pages.

**DRBR6, DRBR5.** Each of these bits, when set, will select one OSD RAM register page.

**DRBR4,DRBR3,DRBR2.** Each of these bits, when set, will select one RAM page.

This register is undefined after reset.

Table 5 summarizes how to set the Data RAM Bank Register in order to select the various banks or pages.

#### Note:

Care is required when handling the DRBR as it is write only. For this reason, it is not allowed to change the DRBR contents while executing interrupts drivers, as the driver cannot save and than restore its previous content. If it is impossible to avoid the writing of this register in interrupts drivers, an image of this register must be saved in a RAM location, and each time the program writes the DRBR it writes also the image register.

The image register must be written first, so if an interrupt occurs between the two instructions the DRBR is not affected.

Table 5. Data RAM Bank Register Set-up

|      | DRBR Value | Selection     |

|------|------------|---------------|

| Hex. | Binary     | Selection     |

| 01h  | 0000 0001  | EEPROM Page 0 |

| 02h  | 0000 0010  | EEPROM Page 1 |

| 03h  | 0000 0011  | EEPROM Page 2 |

| 81h  | 1000 0001  | EEPROM Page 3 |

| 82h  | 1000 0010  | EEPROM Page 4 |

| 83h  | 1000 0011  | EEPROM Page 5 |

| 04h  | 0000 0100  | RAM Page 2    |

| 08h  | 0000 1000  | RAM Page 3    |

| 10h  | 0001 0000  | RAM Page 4    |

| 20h  | 0010 0000  | OSD Page 5    |

| 40h  | 0100 0000  | OSD Page 6    |

#### **EEPROM Description**

The data space of ST638x family from 00h to 3Fh is paged as described in Table 5. 384 bytes of EEPROM located in six pages of 64 bytes (pages 0,1,2,3,4 and 5, see Table 5).

Through the programming of the Data RAM Bank Register (DRBR=E8h) the user can select the bank or page leaving unaffected the way to address the static registers. The way to address the "dynamic" page is to set the DRBR as described in Table 5 (e.g. to select EEPROM page 0, the DRBR has to be loaded with content 01h, see Data RAM/EEPROM/OSD RAM addressing for additional information). Bits 0, 1 and 7 of the DRBR are dedicated to the EEPROM.

The EEPROM pages do not require dedicated instructions to be accessed in reading or writing. The EEPROM is controlled by the EEPROM Control Register (EECR=EAh). Any EEPROM location can be read just like any other data location, also in terms of access time.

To write an EEPROM location takes an average time of 5 ms (10ms max) and during this time the EEPROM is not accessible by the Core. A busy flag can be read by the Core to know the EEPROM status before trying any access. In writing the EEPROM can work in two modes: Byte Mode (BMODE) and Parallel Mode (PMODE). The BMODE is the normal way to use the EEPROM and consists in accessing one byte at a time. The PMODE consists in accessing 8 bytes per time.

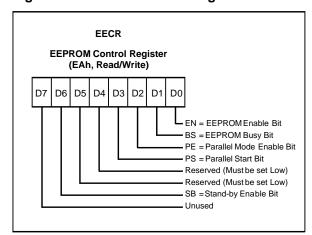

Figure 18. EEPROM Control Register

#### D7. Not used

**SB.** WRITE ONLY. If this bit is set the EEPROM is disabled (any access will be meaningless) and the power consumption of the EEPROM is reduced to the leakage values.

**D5, D4.** Reserved for testing purposes, they must be set to zero.

**PS.** SET ONLY. Once in Parallel Mode, as soon as the user software sets the PS bit the parallel writing of the 8 adjacent registers will start. PS is internally reset at the end of the programming procedure. Note that less than 8 bytes can be written; after parallel programming the remaining undefined bytes will have no particular content.

**PE.** WRITE ONLY. This bit must be set by the user program in order to perform parallel programming (more bytes per time). If PE is set and the "parallel start bit" (PS) is low, up to 8 adjacent bytes can be written at the maximum speed, the content being stored in volatile registers. These 8 adjacent bytes can be considered as row, whose A7, A6, A5, A4, A3 are fixed while A2, A1 and A0 are the changing bytes. PE is automatically reset at the end of any parallel programming procedure. PE can be reset by the user software before starting the programming procedure, leaving unchanged the EEPROM registers.

**BS.** READ ONLY. This bit will be automatically set by the CORE when the user program modifies an EEPROM register. The user program has to test it before any read or write EEPROM operation; any attempt to access the EEPROM while "busy bit" is set will be aborted and the writing procedure in progress completed.

**EN**. WRITE ONLY. This bit MUST be set to one in order to write any EEPROM register. If the user program will attempt to write the EEPROM when EN= "0" the involved registers will be unaffected and the "busy bit" will not be set.

After RESET the content of EECR register will be 00h.

#### Notes:

When the EEPROM is busy (BS="1") the EECR can not be accessed in write mode, it is only possible to read BS status. This implies that as long as the EEPROM is busy it is not possible to change the status of the EEPROM control register. EECR bits 4 and 5 are reserved for test purposes, and must never be set to "1".

Additional Notes on Parallel Mode. If the user wants to perform a parallel programming the first action should be the set to one the PE bit; from this moment the first time the EEPROM will be addressed in writing, the ROW address will be latched and it will be possible to change it only at the end of the programming procedure or by resetting PE without programming the EEPROM. After the ROW address latching the Core can "see" just one EEPROM row (the selected one) and any attempt to write or read other rows will produce errors. Do not read the EEPROM while PE is set.

As soon as PE bit is set, the 8 volatile ROW latches are cleared. From this moment the user can load data in the whole ROW or just in a subset. PS setting will modify the EEPROM registers corresponding to the ROW latches accessed after PE. For example, if the software sets PE and accesses EEPROM in writing at addresses 18h,1Ah,1Bh and then sets PS, these three registers will be modified at the same time; the remaining bytes will have no particular content. Note that PE is internally reset at the end of the programming procedure. This implies that the user must set PE bit between two parallel programming procedures. Anyway the user can set and then reset PE without performing any EEPROM programming. PS is a set only bit and is internally reset at the end of the programming procedure. Note that if the user tries to set PS while PE is not set there will not be any programming procedure and the PS bit will be unaffected. Consequently PS bit can not be set if EN is low. PS can be affected by the user set if, and only if, EN and PE bits are also set to one.

#### **INTERRUPT**

The ST638x Core can manage 4 different maskable interrupt sources, plus one non-maskable interrupt source (top priority level interrupt). Each source is associated with a particular interrupt vector that contains a Jump instruction to the related interrupt service routine. Each vector is located in the Program Space at a particular address (see Table 6). When a source provides an interrupt request, and the request processing is also enabled by the ST638x Core, then the PC register is loaded with the address of the interrupt vector (i.e. of the Jump instruction). Finally, the PC is loaded with the address of the Jump instruction and the interrupt routine is processed.

The relationship between vector and source and the associated priority is hardware fixed for the different ST638x devices. For some interrupt sources it is also possible to select by software the kind of event that will generate the interrupt.

All interrupts can be disabled by writing to the GEN bit (global interrupt enable) of the interrupt option register (address C8h). After a reset, ST638x is in non maskable interrupt mode, so no interrupts will be accepted and NMI flags will be used, until a RETI instruction is executed. If an interrupt is executed, one special cycle is made by the core, during that the PC is set to the related interrupt vector address. A jump instruction at this address has to redirect program execution to the beginning of the related interrupt routine. The interrupt detecting cycle, also resets the related interrupt flag (not available to the user), so that another interrupt can be stored for this current vector, while its driver is under execution.

If additional interrupts arrive from the same source, they will be lost. NMI can interrupt other interrupt routines at any time, while other interrupts cannot interrupt each other. If more than one interrupt is waiting for service, they are executed according to their priority. The lower the number, the higher the priority. Priority is, therefore, fixed. Interrupts are checked during the last cycle of an instruction (RETI included). Level sensitive interrupts have to be valid during this period.

#### **INTERRUPT** (Continued)

Table 6. Interrupt Vectors/Sources Relationships

| Interrupt Source    | Associated<br>Vector          | Vector Address |

|---------------------|-------------------------------|----------------|

| PC6/IRIN<br>Pin (1) | Interrupt<br>Vector # 0 (NMI) | 0FFCh-0FFDh    |

| Timer 2             | Interrupt<br>Vector # 1       | 0FF6h-0FF7h    |

| Vsync               | Interrupt<br>Vector # 2       | 0FF4h-0FF5h    |

| Timer 1             | Interrupt<br>Vector # 3       | 0FF2h-0FF3h    |

| PC4/PWRIN           | Interrupt<br>Vector # 4       | 0FF0h-0FF1h    |

Note: 1. This pin is associated with the NMI Interrupt Vector

#### **Interrupt Vectors/Sources**

The ST638x Core includes 5 different interrupt vectors in order to branch to 5 different interrupt routines. The interrupt vectors are located in the fixed (or static) page of the Program Space.

The interrupt vector associated with the non-maskable interrupt source is named interrupt vector #0. It is located at the (FFCh,FFDh) addresses in the Program Space. This vector is associated with the PC6/IRIN pin.

The interrupt vectors located at addresses (FF6h,FF7h), (FF4h,FF5h), (FF2h,FF3h), (FF0h,FF1h) are named interrupt vectors #1, #2, #3 and #4 respectively. These vectors are associated with TIMER 2 (#1), VSYNC (#2), TIMER 1 (#3) and PC4(PWRIN) (#4).

#### **Interrupt Priority**

The non-maskable interrupt request has the highest priority and can interrupt any other interrupt routines at any time, nevertheless the other interrupts cannot interrupt each other. If more than one interrupt request is pending, they are processed by the ST638x Core according to their priority level: vector #1 has the higher priority while vector #4 the lower. The priority of each interrupt source is hardware fixed.

#### **Interrupt Option Register**

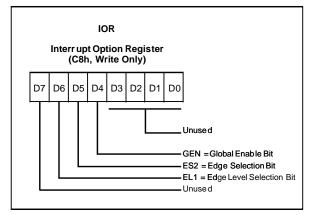

The Interrupt Option Register (IOR register, location C8h) is used to enable/disable the individual interrupt sources and to select the operating mode of the external interrupt inputs. This register can be addressed in the Data Space as RAM location at the C8h address, nevertheless it is write-only register that can not be accessed with single-bit operations. The operating modes of the external interrupt inputs associated to interrupt vectors #1 and #2 are selected through bits 5 and 6 of the IOR register.

Figure 19. Interrupt Option Register

D7. Not used.

**EL1.** This is the Edge/Level selection bit of interrupt #1. When set to one, the interrupt is generated on low level of the related signal; when cleared to zero, the interrupt is generated on falling edge. The bit is cleared to zero after reset.

**ES2.** This is the edge selection bit on interrupt #2. This bit is used on the ST638x devices with on-chip OSD generator for VSYNC detection.

**GEN.** This is the global enable bit. When set to one all interrupts are globally enabled; when this bit is cleared to zero all interrupts are disabled (excluding NMI).

D3 - D0. These bits are not used.

#### **INTERRUPT** (Continued)

#### **Interrupt Procedure**

The interrupt procedure is very similar to a call procedure; the user can consider the interrupt as an asynchronous call procedure. As this is an asynchronous event the user does not know about the context and the time at which it occurred. As a result the user should save all the data space registers which will be used inside the interrupt routines. There are separate sets of processor flags for normal, interrupt and non-maskable interrupt modes which are automatically switched and so these do not need to be saved.

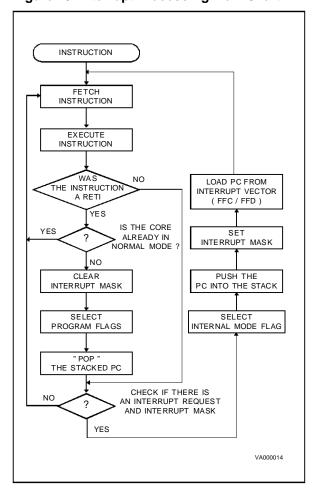

The following list summarizes the interrupt procedure (refer also to Figure 20. Interrupt Processing Flow Chart):

- Interrupt detection

- The flags C and Z of the main routine are exchanged with the flags C and Z of the interrupt routine (resp. the NMI flags)

- The value of the PC is stored in the first level of the stack - The normal interrupt lines are inhibited (NMI still active)

- The edge flip-flop is reset

- The related interrupt vector is loaded in the PC.

- User selected registers are saved inside the interrupt service routine (normally on a software stack)

- The source of the interrupt is found by polling (if more than one source is associated to the same vector)

- Interrupt servicing

- Return from interrupt (RETI)

- Automatically the ST638x core switches back to the normal flags (resp the interrupt flags) and pops the previous PC value from the stack

The interrupt routine begins usually by the identification of the device that has generated the interrupt request. The user should save the registers which are used inside the interrupt routine (that holds relevant data) into a software stack.

After the RETI instruction execution, the Core carries out the previous actions and the main routine can continue.

Figure 20. Interrupt Processing Flow-Chart

#### ST638x Interrupt Details

IR Interrupt (#0). The IRIN/PC6 Interrupt is connected to the first interrupt #0 (NMI, 0FFCh). If the IRINT interrupt is disabled at the Latch circuitry, then it will be high. The #0 interrupt input detects a high to low level. Note that once #0 has been latched, then the only way to remove the latched #0 signal is to service the interrupt. #0 can interrupt the other interrupts. A simple latch is provided from the PC6(IRIN) pin in order to generate the IRINT signal. This latch can be triggered by either the positive or negative edge of IRIN signal. IRINT is inverted with respect to the latch. The latch can be read by software and reset by software.

#### **INTERRUPT** (Continued)

**TIMER 2 Interrupt (#1).** The TIMER 2 Interrupt is connected to the interrupt #1 (0FF6h). The TIMER 2 interrupt generates a low level (which is latched in the timer). Only the low level selection for #1 can be used. Bit 6 of the interrupt option register C8h has to be set.

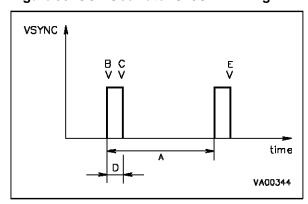

VSYNC Interrupt (#2). The VSYNC Interrupt is connected to the interrupt #2. When disabled the VSYNC INT signal is low. The VSYNC INT signal is inverted with respect to the signal applied to the VSYNC pin. Bit 5 of the interrupt option register C8h is used to select the negative edge (ES2=0) or the positive edge (ES2=1); the edge will depend on the application. Note that once an edge has been latched, then the only way to remove the latched signal is to service the interrupt. Care must be taken not to generate spurious interrupts. This interrupt may be used for synchronize to the VSYNC signal in order to change characters in the OSD only when the screen is on vertical blanking (if desired). This method may also be used to blink characters.

**TIMER 1 Interrupt (#3).** The TIMER 1 Interrupt is connected to the fourth interrupt #3 (0FF2h) which detects a low level (latched in the timer).

**PWR Interrupt (#4).** The PWR Interrupt is connected to the fifth interrupt #4 (0FF0h). If the PWRINT is disabled at the PWR circuitry, then it will be high. The #4 interrupt input detects a low level. A simple latch is provided from the PC4 (PWRIN)pin in order to generate the PWRINT signal. This latch can be triggered by either the positive or negative edge of the PWRIN signal. PWRINT is inverted with respect to the latch. The latch can be reset by software.

Notes Global disable does not reset edge sensitive interrupt flags. These edge sensitive interrupts become pending again when global disabling is released. Moreover, edge sensitive interrupts are stored in the related flags also when interrupts are globally disabled, unless each edge sensitive interrupt is also individually disabled before the interrupting event happens. Global disable is done by clearing the GEN bit of Interrupt option register, while any individual disable is done in the control register of the peripheral. The on-chip Timer peripherals have an interrupt requestflag bit (TMZ), this bit is set to one when the device wants to generate an interrupt request and a mask bit (ETI) that must be set to one to allow the transfer of the flag bit to the Core.

#### RESET

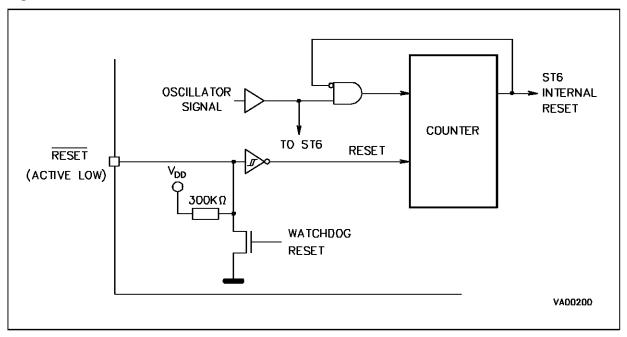

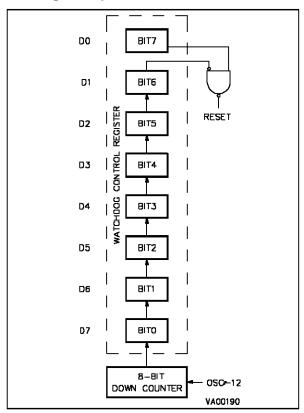

The ST638x devices can be reset in two ways: by the external reset input (RESET) tied low and by the hardware activated digital watchdog peripheral.

#### **RESET Input**

The external active low reset pin is used to reset the ST638x devices and provide an orderly software startup procedure. The activation of the Reset pin may occur at any time in the RUN or WAIT mode. Even short pulses at the reset pin will be accepted since the reset signal is latched internally and is only cleared after 2048 clocks at the oscillator pin. The clocks from the oscillator pin to the reset circuitry are buffered by a schmitt trigger so that an oscillator in start-up conditions will not give spurious clocks. When the reset pin is held low, the external crystal oscillator is also disabled in order to reduce current consumption. The MCU is configured in the Reset mode as long as the signal of the RESET pin is low. The processing of the program is stopped and the standard Input/Outputports (port A, port B and port C) are in the input state. As soon as the level on the reset pin becomes high, the initialization sequence is executed. Refer to the MCU initialization sequence for additional information.

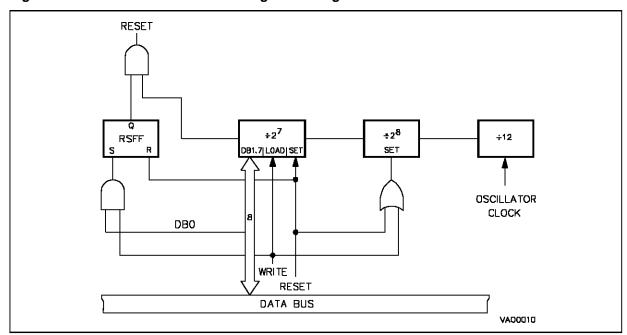

#### **Watchdog Reset**

The ST638x devices are provided with an on-chip hardware activated digital watchdog function in order to provide a graceful recovery from a software upset. If the watchdog register is not refreshed and the end-of-count is reached, then the reset state will be latched into the MCU and an internal circuit pulls down the reset pin. This also resets the watchdog which subsequently turns off the pull-down and activates the pull-up device at the reset pin. This causes the positive transition at the reset pin. The MCU will then exit the reset state after 2048 clocks on the oscillator pin.

#### **Application Notes**

An external resistor between  $V_{DD}$  and the reset pin is not required because an internal pull-up device is provided. The user may prefer to add an external pull-up resistor.

An internal Power-on device does not guarantee that the MCU will exit the reset state when  $V_{DD}$  is above 4.5V and therefore the RESET pin should be externally controlled.

#### **RESET** (Continued)

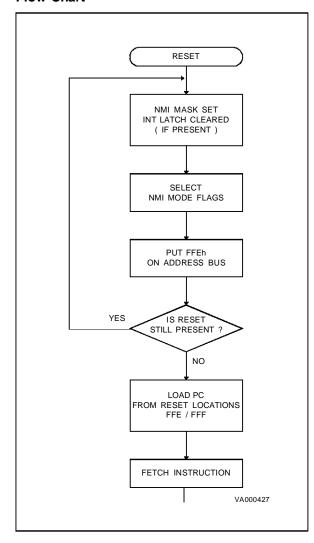

Figure 22. Reset & Interrupt Processing Flow-Chart

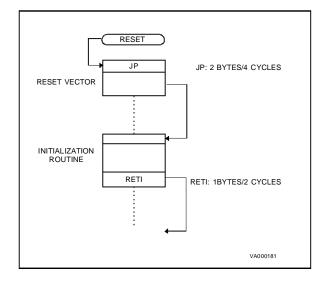

Figure 23. Restart Initialization Program Flow-Chart

#### MCU Initialization Sequence

When a reset occurs the stack is reset to program counter, the PC is loaded with the address of the reset vector (located in the program ROM at addresses FFEh & FFFh). A jump instruction to the beginning of the program has to be written into these locations. After a reset the interrupt mask is automatically activated so that the Core is in non-maskable interrupt mode to prevent false or ghost interrupts during the restart phase. Therefore the restart routine should be terminated by a RETI instruction to switch to normal mode and enable interrupts. If no pending interrupt is present at the end of the reset routine, the ST638x will continue with the instruction after the RETI; otherwise the pending interrupt will be serviced.

#### **RESET Low Power Mode**

When the reset pin is low, the quartz oscillator is Disabled allowing reduced current consumption. When the reset pin is raised the quartz oscillator is enabled and oscillations will start to build up. The internal reset circuitry will count 2048 clocks on the oscillator pin before allowing the MCU to go out of the reset state; the clocks are after a Schmitt trigger so that false or multiple counts are not possible.

#### **WAIT & STOP MODES**

The STOP and WAIT modes have been implemented in the ST638x Core in order to reduce the consumption of the device when the latter has no instruction to execute. These two modes are described in the following paragraphs. On ST638x as the hardware activated digital watchdog function is present the STOP instruction is de-activated and any attempt to execute it will cause the automatic execution of a WAIT instruction.

#### WAIT Mode

The configuration of the MCU in the WAIT mode occurs as soon as the WAIT instruction is executed. The microcontroller can also be considered as being in a "software frozen" state where the Core stops processing the instructions of the routine, the contents of the RAM locations and peripheral registers are saved as long as the power supply voltage is higher than the RAM retention voltage but where the peripherals are still working.

The WAIT mode is used when the user wants to reduce the consumption of the MCU when it is in idle, while not losing count of time or monitoring of external events. The oscillator is not stopped in order to provide clock signal to the peripherals. The timers counting may be enabled (writing the PSI bit in TSCR register) and the timer interrupt may be also enabled before entering the WAIT mode; this allows the WAIT mode to be left when timer interrupt occurs. If the exit from the WAIT mode is performed with a general RESET (either from the activation of the external pin or by watchdog reset) the MCU will enter a normal reset procedure as described in the RESET chapter. If an interrupt is generated during WAIT mode the MCU behaviour depends on the state of the ST638x Core before the initialization of the WAIT sequence, but also of the kind of the interrupt request that is generated. This case will be described in the following paragraphs. In any case, the ST638x Core does not generate any delay after the occurrence of the interrupt because the oscillator clock is still available.

#### **STOP Mode**

On ST638x the hardware watchdog is present and the STOP instruction has been de-activated. Any attempt to execute a STOP will cause the automatic execution of a WAIT instruction.

#### **Exit from WAIT Mode**

The following paragraphs describe the output procedure of the ST638x Core from WAIT mode when an interrupt occurs. It must be noted that the restart

sequence depends on the original state of the MCU (normal, interrupt or non-maskable interrupt mode) before the start of the WAIT sequence, but also of the type of the interrupt request that is generated. In all cases the GEN bit of IOR has to be set to 1 in order to restart from WAIT mode. Contrary to the operation of NMI in the RUN mode, the NMI is masked in WAIT mode if GEN=0.

**Normal Mode.** If the ST638x Core was in the main routine when the WAIT instruction has been executed, the ST638x Core outputs from the wait mode as soon as any interrupt occurs; the related interrupt routine is executed and at the end of the interrupt service routine the instruction that follows the WAIT instruction is executed if no other interrupts are pending.

Non-maskable Interrupt Mode. If the WAIT instruction has been executed during the execution of the non-maskable interrupt routine, the ST638x Core outputs from the wait mode as soon as any interrupt occurs: the instruction that follows the WAIT instruction is executed and the ST638x Core is still in the non-maskable interrupt mode even if another interrupt has been generated.

**Normal Interrupt Mode.** If the ST638x Core was in the interrupt mode before the initialization of the WAIT sequence, it outputs from the wait mode as soon as any interrupt occurs. Nevertheless, two cases have to be considered:

- If the interrupt is a normal interrupt, the interrupt routine in which the WAIT was entered will be completed with the execution of the instruction that follows the WAIT and the ST638x Core is still in the interrupt mode. At the end of this routine pending interrupts will be serviced in accordance to their priority.

- If the interrupt is a non-maskable interrupt, the non-maskable routine is processed at first. Then, the routine in which the WAIT was entered will be completed with the execution of the instruction that follows the WAIT and the ST638x Core is still in the normal interrupt mode.

#### Notes:

If all the interrupt sources are disabled, the restart of the MCU can only be done by a Reset activation. The Wait instruction is not executed if an enabled interrupt request is pending. In the ST638x the hardware activated digital watchdog function is present. As the watchdog is always activated the STOP instruction is de-activated and any attempt to execute the STOP instruction will cause an execution of a WAIT instruction.

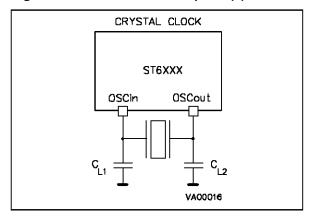

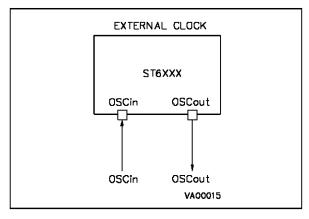

#### ON-CHIP CLOCK OSCILLATOR

The internal oscillator circuit is designed to require a minimum of external components. A crystal quartz, a ceramic resonator, or an external signal (provided to the OSCin pin) may be used to generate a system clock with various stability/cost tradeoffs. The typical clock frequency is 8MHz. Please note that different frequencies will affect the operation of those peripherals (D/As, SPI) whose reference frequencies are derived from the system clock.

The different clock generator options connection methods are shown in Figures 24 and 25. One machine cycle takes 13 oscillator pulses; 12 clock pulses are needed to increment the PC while and additional 13th pulse is needed to stabilize the internal latches during memory addressing. This means that with a clock frequency of 8MHz the machine cycle is 1.625us.

The crystal oscillator start-up time is a function of many variables: crystal parameters (especially RS), oscillator load capacitance (CL), IC parameters, ambient temperature, and supply voltage. It must be observed that the crystal or ceramic leads and circuit connections must be as short as possible. Typical values for CL1 and CL2 are in the range of 15pF to 22pF but these should be chosen based on the crystal manufacturers specification. Typical input capacitance for OSCin and OSCout pins is 5pF.

The oscillator output frequency is internally divided by 13 to produce the machine cycle and by 12 to produce the Timer and the Watchdog clock. A byte cycle is the smallest unit needed to execute any operation (i.e., increment the program counter). An instruction may need two, four, or five byte cycles to be executed (See Table 7).

Table 7. Intructions Timing with 8MHz Clock

| •                          |          |                   |

|----------------------------|----------|-------------------|

| Instruction Type           | Cycles   | Execution<br>Time |

| Branch if set/reset        | 5 Cycles | 8.125µs           |

| Branch & Subroutine Branch | 4 Cycles | 6.50μs            |

| Bit Manipulation           | 4 Cycles | 6.50µs            |

| Load Instruction           | 4 Cycles | 6.50μs            |

| Arithmetic & Logic         | 4 Cycles | 6.50μs            |

| Conditional Branch         | 2 Cycles | 3.25µs            |

| Program Control            | 2 Cycles | 3.25µs            |

Figure 24. Clock Generator Option (1)

Figure 25. Clock Generator Option (2)

Figure 26. OSCIN, OSCOUT Diagram

#### INPUT/OUTPUT PORTS

The ST638x microcontrollers use three standard I/O ports (A,B,C) with up to eight pins on each port; refer to the device pin configurations to see which pins are available.

Each line can be individually programmed either in the input mode or the output mode as follows by software.

- Output

- Input with on-chip pull-up resistor (selected by software)

- Input without on-chip pull-up resistor (selected by software)

Note: pins with 12V open-drain capability do not have pull-up resistors.

In output mode the following hardware configurations are available:

- Open-drain output 12V (PA4-PA7, PC4-PC7)

- Open-drain output 5V (PC0-PC3)

- Push-pull output (PA0-PA3, PB0-PB6)

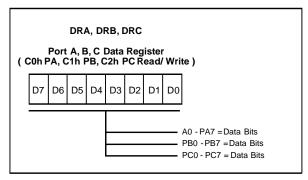

The lines are organized in three ports (port A,B,C). The ports occupy 6 registers in the data space. Each bit of these registers is associated with a particular line (for instance, the bits 0 of the Port A Data and Direction registers are associated with the PA0 line of Port A).

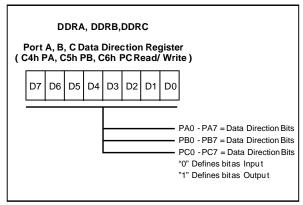

There are three Data registers (DRA, DRB, DRC). that are used to read the voltage level values of the lines programmed in the input mode, or to write the logic value of the signal to be output on the lines configured in the output mode. The port Data Registers can be read to get the effective logic levels of the pins, but they can be also written by the user software, in conjunction with the related Data Direction Register, to select the different input mode options. Single-bit operations on I/O registers (bit set/reset instructions) are possible but care is necessary because reading in input mode is made from I/O pins and therefore might be influenced by the external load, while writing will directly affect the Port data register causing an undesired changes of the input configuration. The three Data Direction registers (DDRA, DDRB, DDRC) allow the selection of the direction of each pin (input or output).

All the I/O registers can be read or written as any other RAM location of the data space, so no extra RAM cell is needed for port data storing and manipulation. During the initialization of the MCU, all the I/O registers are cleared and the input mode with pull-up is selected on all the pins thus avoiding pin conflicts (with the exception of PC2 that is set in output mode and is set high ie. high impedance).

#### **Details of I/O Ports**

When programmed as an input a pull-up resistor (if available) can be switched active under program control. When programmed as an output the I/O port will operate either in the push-pull mode or the open-drain mode according to the hardware fixed configuration as specified below.

**Port A.** PA0-PA3 are available as push-pull when outputs. PA4-PA7 are available as open-drain (no push-pull programmability) capable of withstanding 12V (no resistive pull-up in input mode). PA6-PA7 has been specially designed for higher driving capability and are able to sink 25mA with a maximum Vol. of 1V.

**Port B.** All lines are configured as push-pull when outputs.

**Port C.** PC0-PC3 are available as open-drain capable of withstanding a maximum  $V_{DD}+0.3V$ . PC4-PC7 are available as open-drain capable of withstanding 12V (no resistive pull-up in input mode). Some lines are also used as I/O buffers for signals coming from the on-chip SPI.

In this case the final signal on the output pin is equivalent to a wired AND with the programmed data output.

If the user needs to use the serial peripheral, the I/O line should be set in output mode while the open-drain configuration is hardware fixed; the corresponding data bit must set to one. If the latched interrupt functions are used (IRIN, PWRIN) then the corresponding pins should be set to input mode.

On ST638x the I/O pins with double or special functions are:

- PC0/SCL (connected to the SPI clock signal)

- PC1/SDA (connected to the SPI data signal)

- PC3/SEN (connected to the SPI enable signal)

- PC4/PWRIN (connected to the PWRIN interrupt latch)

- PC6/IRIN (connected to the IRIN interrupt latch)

All the Port A,B and C I/O lines have Schmitt-trigger input configuration with a typical hysteresis of 1V.

#### **INPUT/OUTPUT PORTS** (Continued)

Table 8. I/O Port Options Selection

| DDR | DR | Mode   | Option                           |  |

|-----|----|--------|----------------------------------|--|

| 0   | 0  | Input  | With on-chip pull-up<br>resistor |  |

| 0   | 1  | Input  | Without on-chip pull-up resistor |  |

| 1   | Х  | Output | Open-drain or Push-Pull          |  |

Note: X: Means don't care.

Figure 27. Port A, B, C Data Register

**PA7-PA0.** These are the I/O port A data bits. Reset at power-on.

**PB7-PB0.** These are the I/O port B data bits. Reset at power-on.

**PC7-PC0.** Set to 04h at power-on. Bit 2 (PC2 pin) is set to one (open drain therefore high impedence).

#### I/O Pin Programming

Each pin can be individually programmed as input or output with different input and output configurations. This is achieved by writing to the relevant bit in the data (DR) and data direction register (DDR). Table 8 shows all the port configurations that can be selected by the user software.

Figure 28. Port A, B, C Data Register

**PA7-PA0.** These are the I/O port A data direction bits. When a bit is cleared to zero the related I/O line is in input mode, if bit is set to one the related I/O line is in output mode. Reset at power-on.

**PB7-PB0.** These are the I/O port B data direction bits. When a bit is cleared to zero the related I/O line is in input mode, if bit is set to one the related I/O line is in output mode. Reset at power-on.

**PC7-PC0.** These are the I/O port C data direction bits. When a bit is cleared to zero the related I/O line is in input mode, if bit is set to one the related I/O line is in output mode. Set to 04h at power-on. Bit 2 (PC2 pin) is set to one (output mode selected).

#### **INPUT/OUTPUT PORTS** (Continued)

#### **Input/Output Configurations**

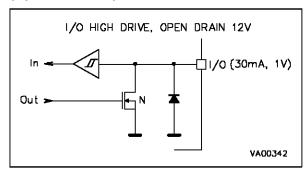

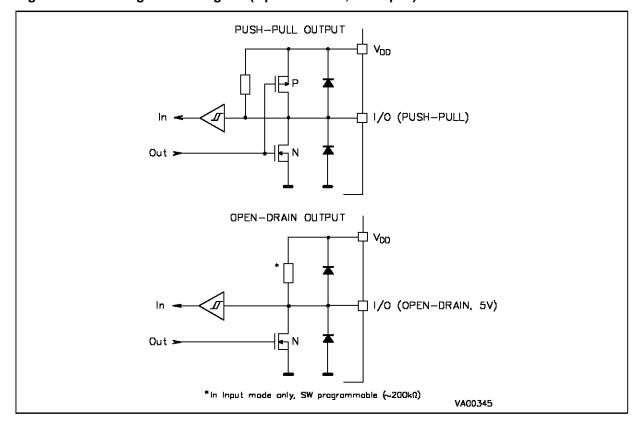

The following schematics show the I/O lines hardware configuration for the different options. Figure 29 shows the I/O configuration for an I/O pin with open-drain 12V capability (standard drive and high drive). Figure 30 shows the I/O configuration for an I/O pin with push-pull and with open drain 5V capability.

# Figure 29. I/O Configuration Diagram (Open Drain 12V)

#### Notes:

The WAIT instruction allows the ST638x to be used in situations where low power consumption is needed. This can only be achieved however if the I/O pins either are programmed as inputs with well defined logic levels or have no power consuming resistive loads in output mode. As the same die is used for the different ST638x versions the unavailable I/O lines of ST638x should be programmed in output mode.

Single-bit operations on I/O registers are possible but **care is necessary** because reading in input mode is made from I/O pins while writing will directly affect the Port data register causing an undesired changes of the input configuration.

Figure 30. I/O Configuration Diagram (Open Drain 5V, Push-pull)

#### **TIMERS**

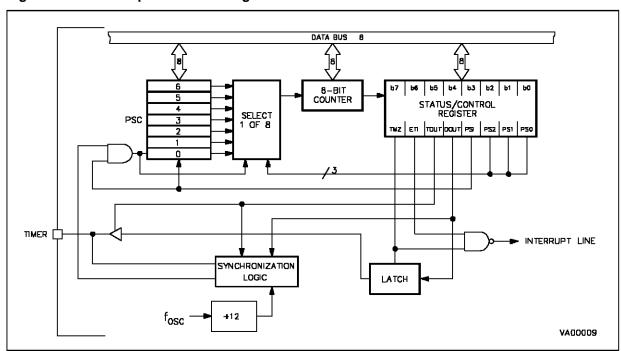

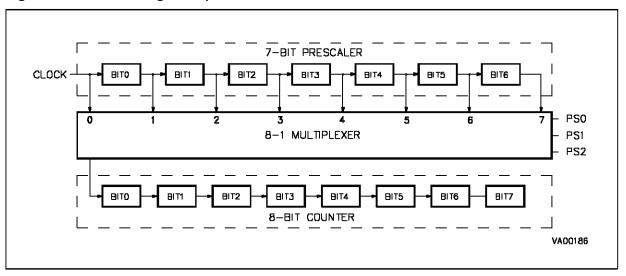

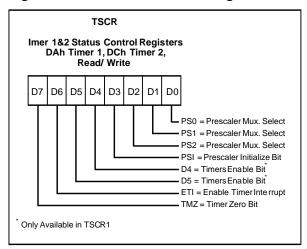

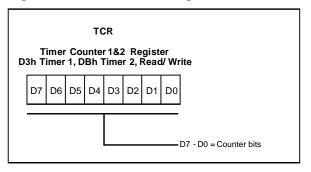

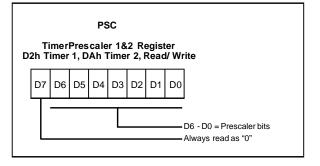

The ST638x devices offer two on-chip Timer peripherals consisting of an 8-bit counter with a 7-bit programmable prescaler, thus giving a maximum count of 2<sup>15</sup>, and a control logic that allows configuring the peripheral operating mode. Figure 30 shows the timer block diagram. The content of the 8-bit counters can be read/written in the Timer/Counter registers TCR that can be addressed in the data space as RAM location at addresses D3h (Timer 1) and DBh (Timer 2). The state of the 7-bit prescaler can be read in the PSC register at addresses D2h (Timer 1) and DAh (Timer 2). The control logic is managed by TSCR registers at D4h (Timer 1) and DCh (Timer 2) addresses as described in the following paragraphs.

The following description applies to both Timer 1 and Timer 2. The 8-bit counter is decrement by the output (rising edge) coming from the 7-bit prescaler and can be loaded and read under program control. When it decrements to zero then the TMZ (timer zero) bit in the TSCR is set to one. If the ETI (enable timer interrupt) bit in the TSCR is also set to one an interrupt request, associated to interrupt vector #3 (for Timer 1) and #1 for Timer 2, is generated. The interrupt of the timer can be used to exit the MCU from the WAIT mode.

The prescaler decrements on rising edge. The prescaler input is the oscillator frequency divided by 12.

Depending on the division factor programmed by PS2/PS1/PS0 (see table 9) bits in the TSCR, the clock input of the timer/counter register is multiplexed to different sources.

On division factor 1, the clock input of the prescaler is also that of timer/counter, on factor 2, bit 0 of prescaler register is connected to the clock input of TCR.

This bit changes its state with the half frequency of prescaler clock input. On factor 4, bit 1 of PSC is connected to clock input of TCR, and so on. On division factor 128, the MSB bit 6 of PSC is connected to clock input of TCR. The prescaler initialize bit (PSI) in the TSCR register must be set to one to allow the prescaler (and hence the counter) to start. If it is cleared to zero then all of the prescaler bits are set to one and the counter is inhibited from counting.

The prescaler can be given any value between 0 and 7Fh by writing to the related register address, if bit PSI in the TSCR register is set to one. The tap of the prescaler is selected using the PS2/PS1/PS0 bits in the control register. Figure 31 shows the timer working principle.

Figure 30. Timer Peripheral Block Diagram

#### TIMERS (Continued)

Figure 31. Timer Working Principle

#### Timer Operating Modes

As on ST638x devices the external TIMER pin is not available the only allowed operating mode is the output mode that have to be selected by setting to 1 bit 4 and by clearing to 0 bit 5 in the TSCR1 register. This procedure will enable both Timer 1 and Timer 2.

Output Mode (TSCR1 D4 = 1, TSCR1 D5 = 0). On this mode the timer prescaler is clocked by the prescaler clock input (OSC/12). The user can select the desired prescaler division ratio through the PS2/PS1/PS0 bits. When TCR count reaches 0, it sets the TMZ bit in the TSCR.

The TMZ bit can be tested under program control to perform timer functions whenever it goes high. Bit D4 and D5 on TSCR2 (Timer 2) register are not implemented.

#### **Timer Interrupt**

When the counter register decrements to zero and the software controlled ETI (enable timer interrupt) bit is set to one then an interrupt request associated to interrupt vector #3 (for Timer 1) and to interrupt vector #1 (for Timer 2) is generated. When the counter decrements to zero also the TMZ bit in the TSCR register is set to one.

#### Notes

TMZ is set when the counter reaches 00h; however, it may be set by writing 00h in the TCR register or setting the bit 7 of the TSCR register. TMZ bit must be cleared by user software when servicing the timer interrupt to avoid undesired interrupts when leaving the interrupt service routine. After reset, the 8-bit counter register is loaded to FFh while the 7-bit prescaler is loaded to 7Fh, and the TSCR register is cleared which means that timer is stopped (PSI=0) and timer interrupt disabled.

A write to the TCR register will predominate over the 8-bit counter decrement to 00h function, i.e. if a write and a TCR register decrement to 00h occur simultaneously, the write will take precedence, and the TMZ bit is not set until the 8-bit counter reaches 00h again. The values of the TCR and the PSC registers can be read accurately at any time.

#### TIMERS (Continued)

Figure 32. Timer Status Control Registers

**TMZ.** Low-to-high transition indicates that the timer count register has decrement to zero. This bit must be cleared by user software before to start with a new count.

**ETI.** This bit, when set, enables the timer interrupt (vector #3 for Timer 1, vector #1 for Timer 2) request. If ETI=0 the timer interrupt is disabled. If ETI=1 and TMZ=1 an interrupt request is generated.

**D5.** This is the timers enable bit D5. It must be cleared to 0 together with a set to 1 of bit D4 to enable both Timer 1 and Timer 2 functions. It is not implemented on TSCR2 register.

**D4.** This is the timers enable bit D4. This bit must be set to 1 together with a clear to 0 of bit D5 to enable both Timer 1 and Timer 2 functions. It is not implemented on TSCR2 register.

| D5 | D4 | Timers   |

|----|----|----------|

| 0  | 0  | Disabled |

| 0  | 1  | Enabled  |

| 1  | Х  | Reserved |

**PS1.** Used to initialize the prescaler and inhibit its counting while PSI = 0 the prescaler is set to 7Fh and the counter is inhibited. When PSI = 1 the prescaler is enabled to count downwards. As long as PSI= 0 both counter and prescaler are not running.

**PS2-PS0.** These bits select the division ratio of the prescaler register. (see table 9)

The TSCR1 and TSCR2 registers are cleared on reset. The correct D4-D5 combination must be written in TSCR1 by user's software to enable the operation of Timer 1 and Timer 2.

**Table 9. Prescaler Division Factors**

| PS2 | PS1 | PS0 | Divided By |

|-----|-----|-----|------------|

| 0   | 0   | 0   | 1          |

| 0   | 0   | 1   | 2          |

| 0   | 1   | 0   | 4          |

| 0   | 1   | 1   | 8          |

| 1   | 0   | 0   | 16         |

| 1   | 0   | 1   | 32         |

| 1   | 1   | 0   | 64         |

| 1   | 1   | 1   | 128        |

Figure 33. Timer Counter Registers

Figure 34. Timer Counter Registers

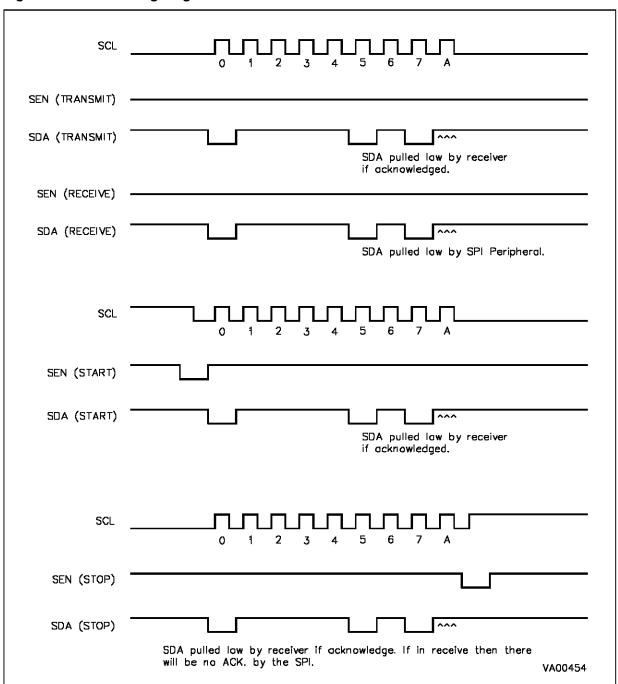

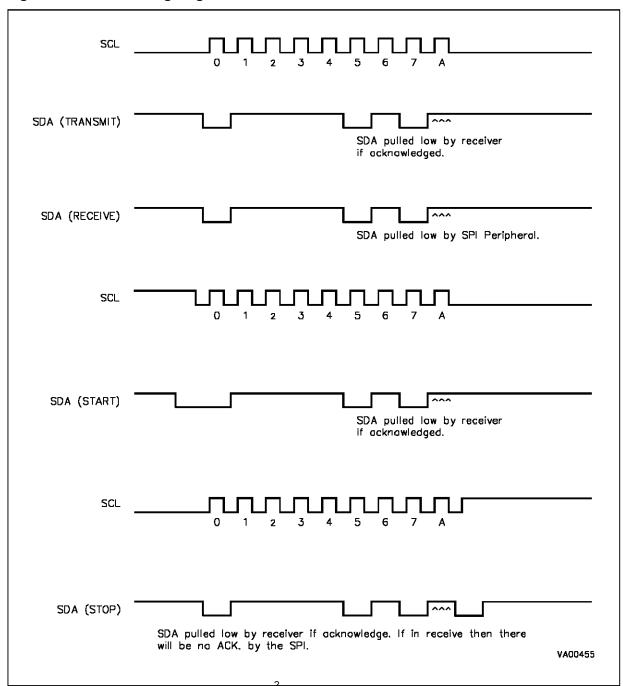

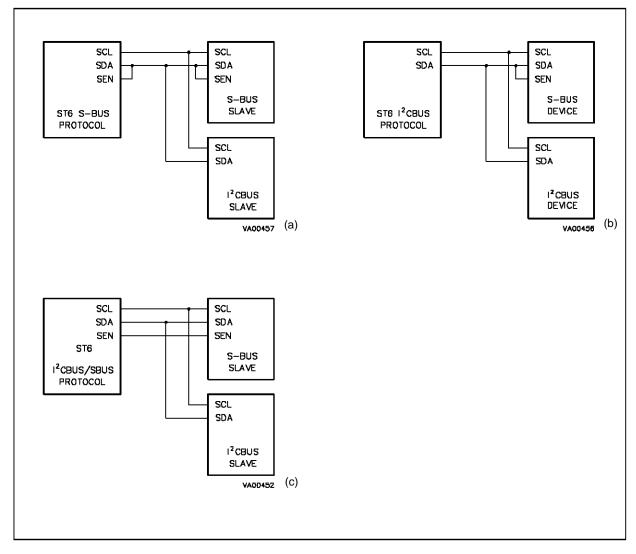

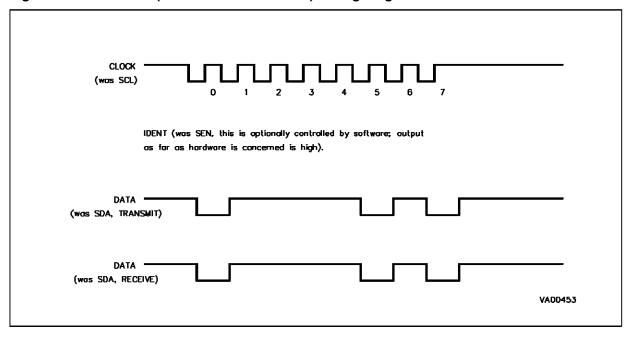

# HARDWARE ACTIVATED DIGITAL WATCHDOG FUNCTION